M68HC11

Reference Manual

# M68HC11 Microcontrollers

M68HC11RM/D Rev. 6.1

Copyright Freescale Semiconductor, Inc. 2002, 2007

# M68HC11

#### **Reference Manual**

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://www.freescale.com

The following revision history table summarizes changes contained in this document. For your convenience, the page number designators have been linked to the appropriate location.

#### **Revision History**

| Date              | Revision<br>Level | Description                                                                                                                     | Page<br>Number(s) |

|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------|-------------------|

| June,             | 4                 | Reformatted to meet current publications standards                                                                              | ,                 |

| 2001              |                   | Index — Updated                                                                                                                 | 631               |

| February,<br>2002 | 5                 | Figure 9-4. Baud Rate Control Register (BAUD) — Address designation corrected to \$102B                                         | 327               |

|                   |                   | ADD Instruction —Corrected table head from ADCA to ADDA                                                                         | 496               |

|                   |                   | AND Instruction — Corrected table head from ADCA to ANDA                                                                        | 498               |

|                   |                   | ASL Instruction —Corrected table heads ASLA (IMM) to ASLA (INH) and ASLB (DIR) to ASLB (INH)                                    | 499               |

|                   |                   | ASR Instruction — Corrected table heads ASRA (IMM) to ASRA (INH) and ASRB (DIR) to ASRB (INH)                                   | 501               |

| April,<br>2002    | 6                 | BIT Instruction — Corrected second table entry for Data under  BITA (IND,Y) from AS to A5 and under BITB (IND,Y) from ES to  E5 | 510               |

|                   |                   | CLR Instruction — Corrected table head from CLRA (IMM) to CLRA (INH) and CLRB (DIR) to CLRB (INH)                               | 529               |

|                   |                   | STY Instruction — Corrected second table entry for Data under STY (IND,X) EE to EF                                              | 584               |

|                   |                   | WAI Instruction — Changed I bit designation from 1 to —                                                                         | 598               |

|                   |                   |                                                                                                                                 |                   |

### **List of Sections**

| Section 1. General Description27                         |

|----------------------------------------------------------|

| Section 2. Pins and Connections35                        |

| Section 3. Configuration and Modes of Operation85        |

| Section 4. On-Chip Memory                                |

| Section 5. Resets and Interrupts                         |

| Section 6. Central Processor Unit (CPU)197               |

| Section 7. Parallel Input/Output229                      |

| Section 8. Synchronous Serial Peripheral Interface291    |

| Section 9. Asynchronous Serial  Communications Interface |

| Section 10. Main Timer and Real-Time Interrupt 367       |

| Section 11. Pulse Accumulator                            |

| Section 12. Analog-to-Digital Converter System 459       |

| Appendix A. Instruction Set Details487                   |

| Appendix B. Bootloader Listings603                       |

| Index                                                    |

## List of Sections

#### **Table of Contents**

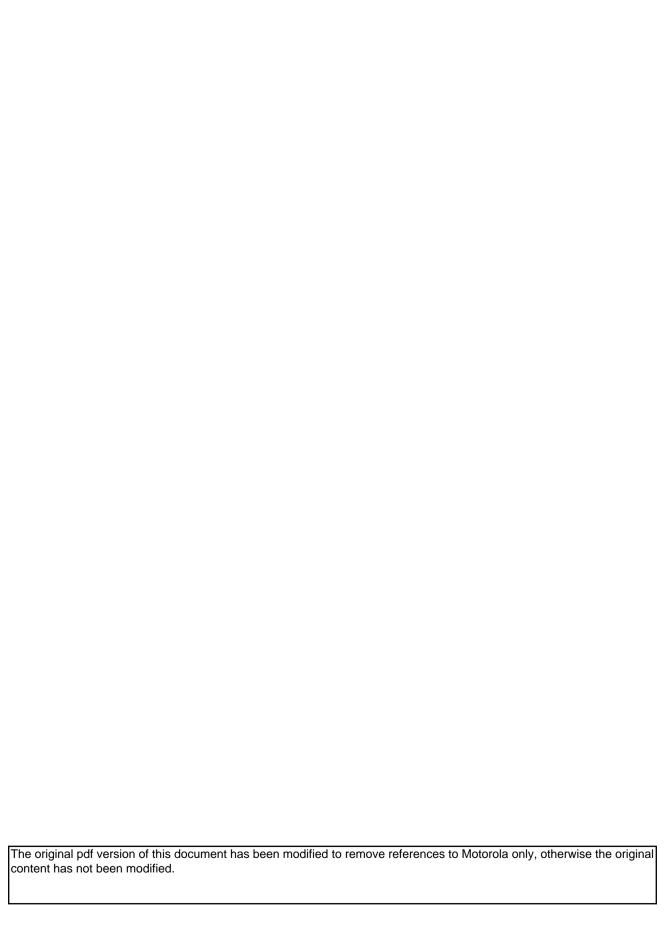

#### **Section 1. General Description**

| 1.1                                                                            | Contents                                                                                                                                    | 27                               |

|--------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1.2                                                                            | Introduction                                                                                                                                | 27                               |

| 1.3                                                                            | General Description of the MC68HC11A8                                                                                                       | 28                               |

| 1.4                                                                            | Programmer's Model                                                                                                                          | 29                               |

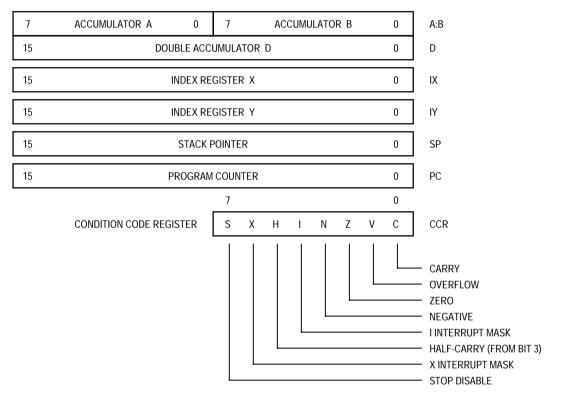

| 1.5                                                                            | Product Derivatives                                                                                                                         | 32                               |

|                                                                                | Section 2. Pins and Connections                                                                                                             |                                  |

| 2.1                                                                            | Contents                                                                                                                                    | 35                               |

| 2.2                                                                            | Introduction                                                                                                                                | 36                               |

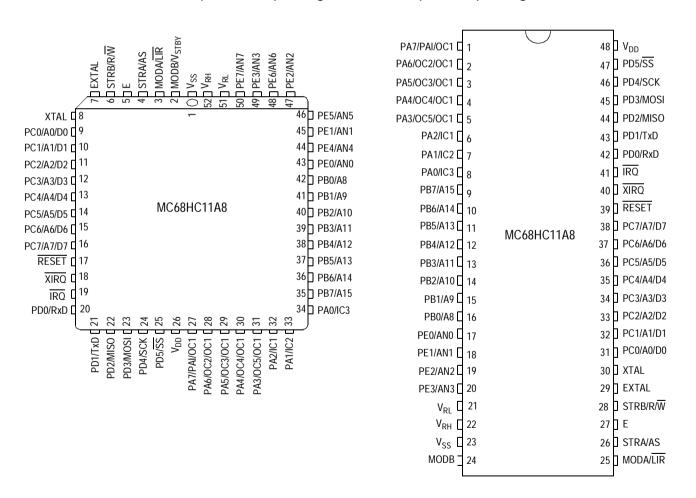

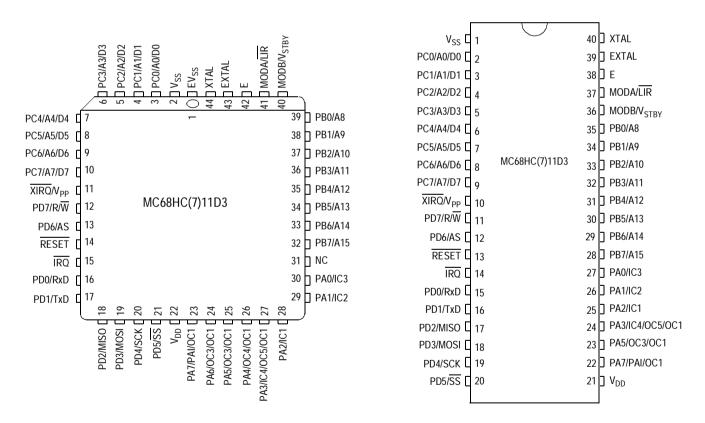

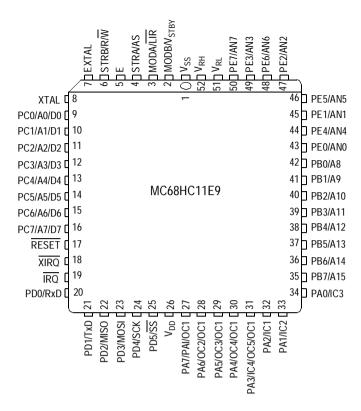

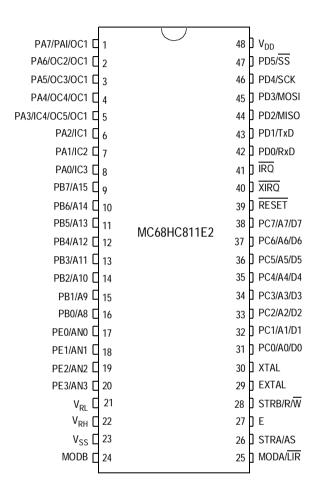

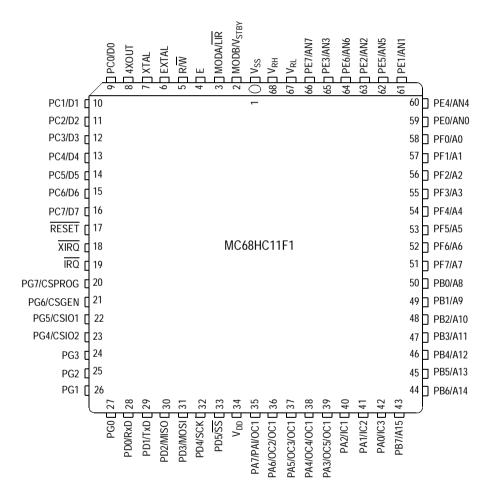

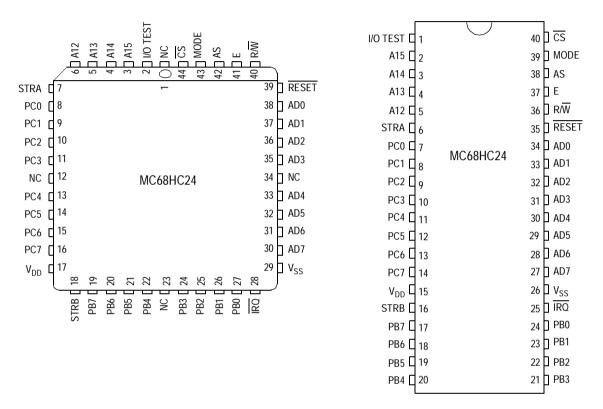

| 2.3<br>2.3.1<br>2.3.2<br>2.3.3<br>2.3.4<br>2.3.5<br>2.3.6                      | Packages and Pin Names  MC68HC11A8  MC68HC11D3/MC68HC711D3  MC68HC11E9/MC68HC711E9  MC68HC811E2  MC68HC11F1  MC68HC24 Port Replacement Unit | 38<br>39<br>40<br>41             |

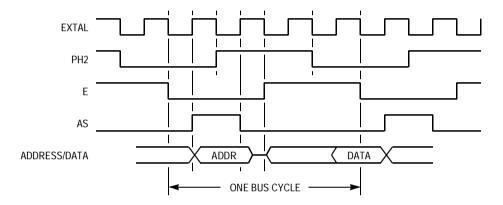

| 2.4<br>2.4.1<br>2.4.2<br>2.4.3<br>2.4.4<br>2.4.4.<br>2.4.4.<br>2.4.4.<br>2.4.5 | Using Crystal Oscillator Outputs                                                                                                            | 45<br>46<br>50<br>55<br>55<br>56 |

M68HC11 — Rev. 6.1

Reference Manual

| 2.4.6          | Interrupt Pins (XIRQ and IRQ)                         | .58        |

|----------------|-------------------------------------------------------|------------|

| 2.4.7          | A/D Reference and Port E Pins                         | <b>5</b> 0 |

| 2.4.8          | (V <sub>REFL</sub> , V <sub>REFH</sub> , and PE7–PE0) |            |

| 2.4.9          | Serial Port D Pins                                    |            |

| 2.4.10         |                                                       |            |

| 2.5            | Termination of Unused Pins                            | .64        |

| 2.6            | Avoidance of Pin Damage                               | .66        |

| 2.6.1          | Zap and Latchup                                       | .67        |

| 2.6.2          | Protective Interface Circuits                         | .68        |

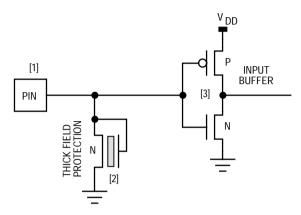

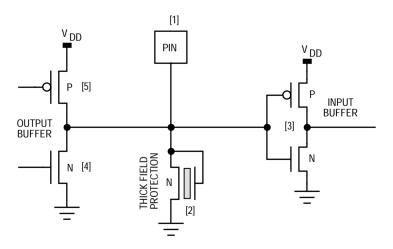

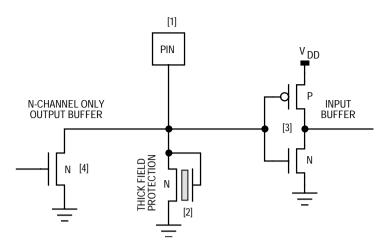

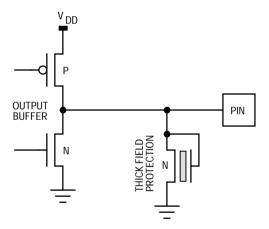

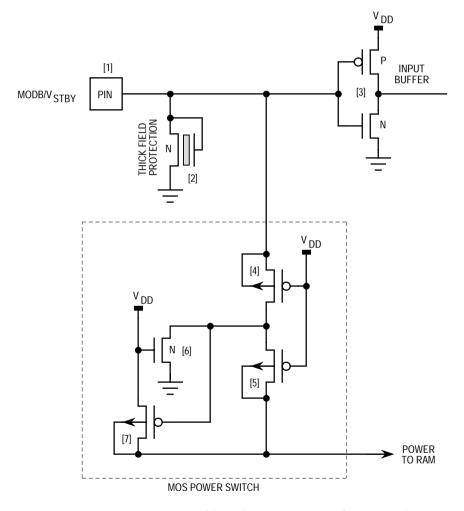

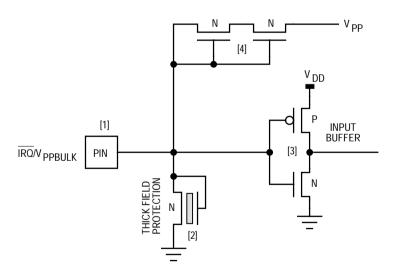

| 2.6.3          | Internal Circuitry — Digital Input-Only Pin           |            |

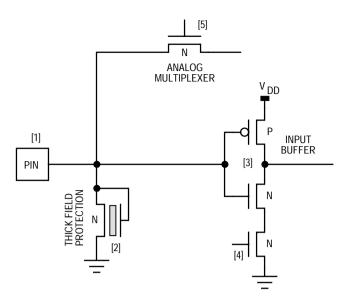

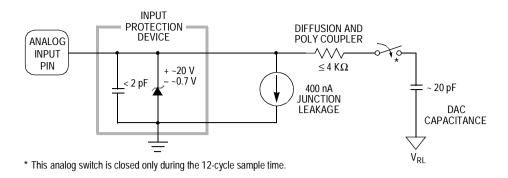

| 2.6.4          | Internal Circuitry — Analog Input-Only Pin            |            |

| 2.6.5          | Internal Circuitry — Digital I/O Pin                  |            |

| 2.6.6          | Internal Circuitry — Input/Open-Drain-Output Pin      |            |

| 2.6.7<br>2.6.8 | Internal Circuitry — Digital Output-Only Pin          |            |

| 2.6.9          | Internal Circuitry — MODB/V <sub>STBY</sub> Pin       |            |

|                |                                                       |            |

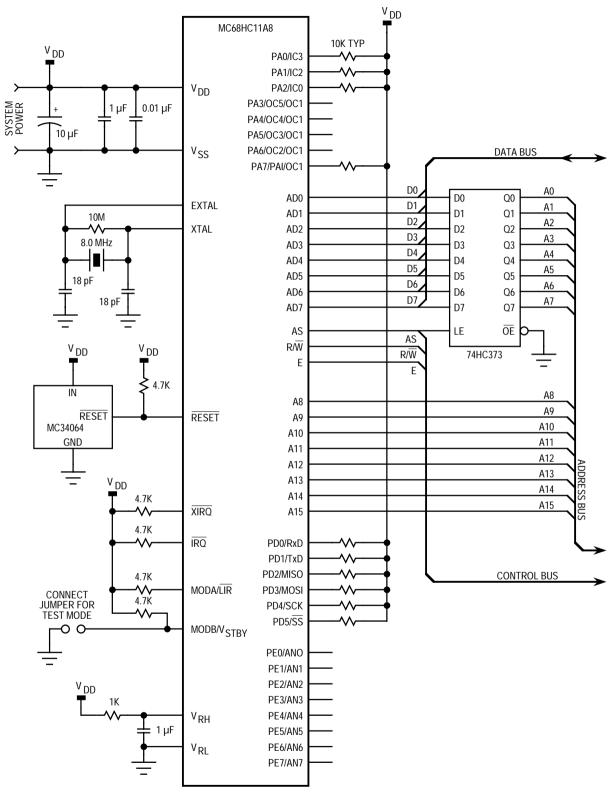

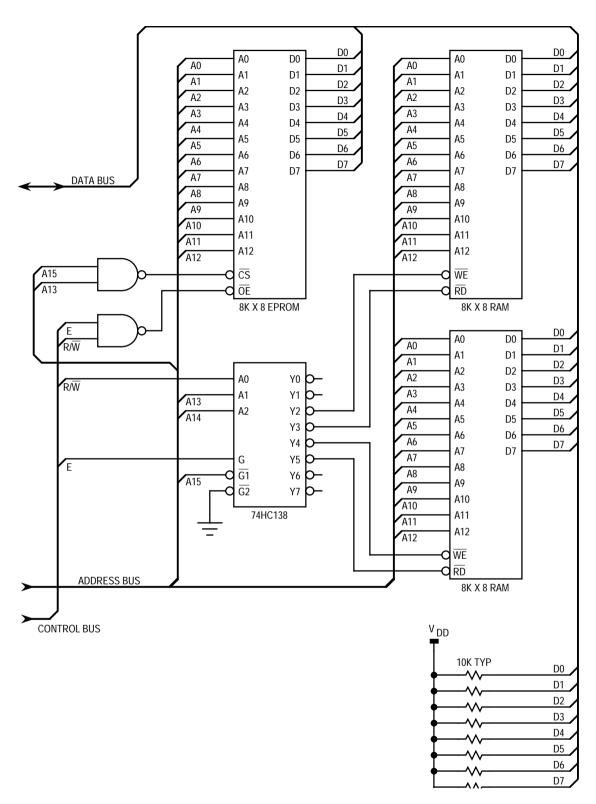

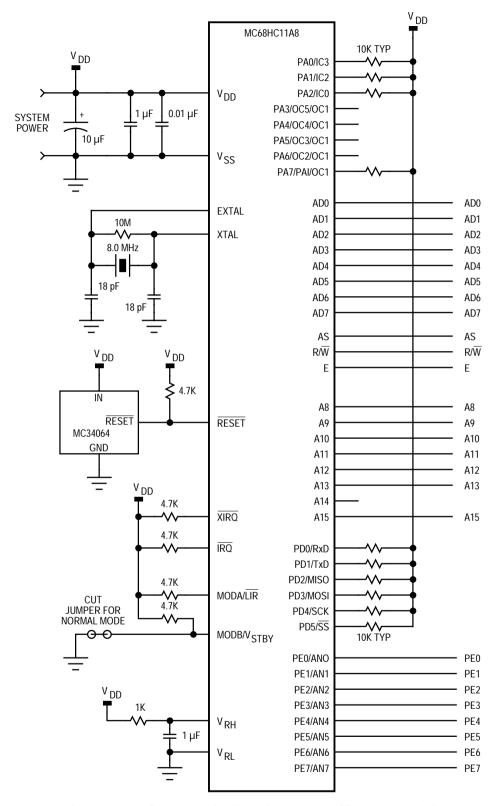

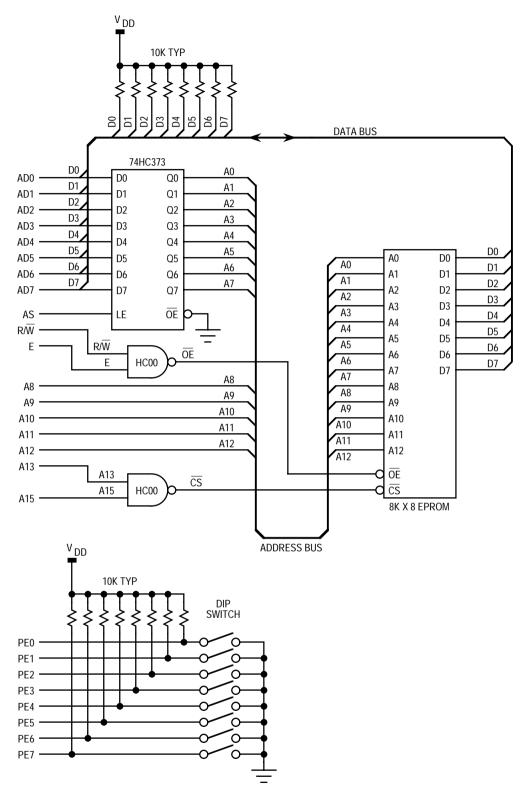

| 2.7            | Typical Expanded Mode System Connections              | .77        |

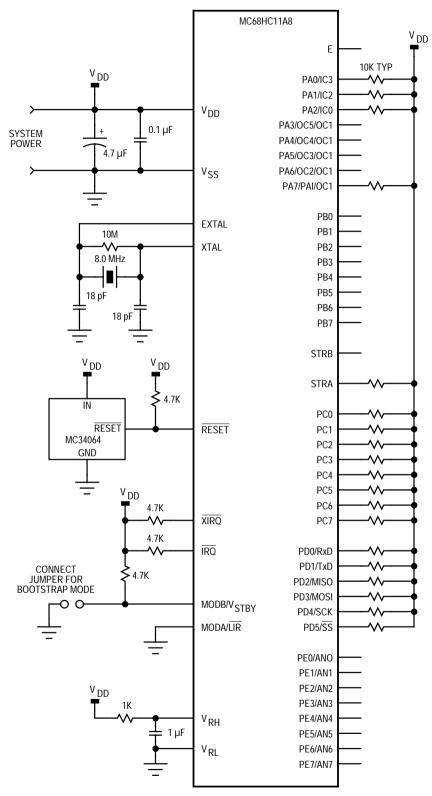

| 2.8            | Typical Single-Chip Mode System Connections           | .81        |

| 2.9            | System Development and Debug Features                 | .82        |

| 2.9.1          | Load Instruction Register (LIR)                       |            |

| 2.9.2          | Internal Read Visibility (IRV)                        |            |

| 2.9.3          | MC68HC24 Port Replacement Unit (PRU)                  | .83        |

| S              | Section 3. Configuration and Modes of Operation       |            |

| 3.1            | Contents                                              | .85        |

| 3.2            | Introduction                                          | .86        |

| 3.3            | Hardware Mode Selection                               | .86        |

| 3.3.1          | Hardware Mode Select Pins                             |            |

| 3.3.2          | Mode Control Bits in the HPRIO Register               |            |

| 3.4            | EEPROM-Based Configuration (CONFIG) Register          | .89        |

| 3.4.1          | Operation of CONFIG Mechanism                         |            |

| 3.4.2          | CONFIG Register                                       |            |

|                |                                                       |            |

| 3.5<br>3.5.1<br>3.5.2<br>3.5.3                                        | Protected Control Register Bits                              | 95<br>98                         |

|-----------------------------------------------------------------------|--------------------------------------------------------------|----------------------------------|

| 3.6<br>3.6.1<br>3.6.2                                                 | Normal MCU Operating Modes                                   | 01                               |

| 3.7<br>3.7.1<br>3.7.2<br>3.7.3<br>3.7.4<br>3.7.4.<br>3.7.4.<br>3.7.4. | <ul> <li>Executing User Programs in Bootstrap Mode</li></ul> | 04<br>07<br>08<br>09<br>10<br>11 |

| 3.8                                                                   | Test and Bootstrap Mode Applications1                        | 14                               |

| 3.9                                                                   | Example 3-1: Programming CONFIG  (Uses Special Test Mode)    | 15                               |

| 4.1                                                                   | Contents                                                     | 21                               |

| 4.2                                                                   | Introduction                                                 | 22                               |

| 4.3                                                                   | Read-Only Memory (ROM)                                       | 22                               |

| 4.4<br>4.4.1<br>4.4.2                                                 | Random-Access Memory (RAM)                                   | 24                               |

| 4.5<br>4.5.1<br>4.5.2<br>4.5.3<br>4.5.4                               | Electrically Erasable Programmable ROM (EEPROM)              | 27<br>29<br>34                   |

|                                                                       |                                                              |                                  |

| 4.5.5    | Programming/Erasing Procedures                | .137 |

|----------|-----------------------------------------------|------|

| 4.5.5.1  | · · · · · · · · · · · · · · · · · · ·         |      |

| 4.5.5.2  | Bulk Erase                                    | .138 |

| 4.5.5.3  | Row Erase                                     | .139 |

| 4.5.5.4  | Byte Erase                                    | .139 |

| 4.5.5.5  | <b>3</b>                                      |      |

| 4.5.6    | Optional EEPROM Security Mode                 | .140 |

| 4.6 E    | EEPROM Application Information                | .143 |

| 4.6.1    | Conditions and Practices to Avoid             |      |

| 4.6.2    | Using EEPROM to Select Product Options        | .146 |

| 4.6.3    | Using EEPROM for Setpoint                     |      |

|          | and Calibration Information                   | .146 |

| 4.6.4    | Using EEPROM during Product Development       | .148 |

| 4.6.5    | Logging Data                                  | .148 |

| 4.6.6    | Self-Adjusting Systems Using EEPROM           |      |

| 4.6.7    | Software Methods to Extend Life Expectancy    | .150 |

|          |                                               |      |

|          | Section 5. Resets and Interrupts              |      |

| 5.1      | Contents                                      | .159 |

| 5.2 I    | Introduction                                  | .160 |

| 5.3 I    | Initial Conditions Established During Reset   | .161 |

| 5.3.1    | System Initial Conditions                     |      |

| 5.3.1.1  |                                               |      |

| 5.3.1.2  |                                               |      |

| 5.3.1.3  | •                                             |      |

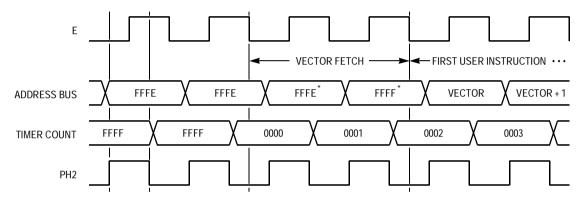

| 5.3.1.4  | Timer                                         | .163 |

| 5.3.1.5  | Real-Time Interrupt                           | .163 |

| 5.3.1.6  | Pulse Accumulator                             | .163 |

| 5.3.1.7  | Computer Operating Properly (COP) Watchdog    | .164 |

| 5.3.1.8  | Serial Communications Interface (SCI)         | .164 |

| 5.3.1.9  | Serial Peripheral Interface (SPI)             | .164 |

| 5.3.1.10 | 0 Analog-to-Digital (A/D) Converter           | .164 |

| 5.3.1.1  |                                               |      |

| 5.3.2    | CONFIG Register Allows Flexible Configuration | .165 |

| 5.3.3    | Mode of Operation Established                 |      |

| 5.3.4    | Program Counter Loaded with Reset Vector      | .167 |

|          |                                               |      |

| Causes of Reset                                | 69                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Clock Monitor Reset                            | 72                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

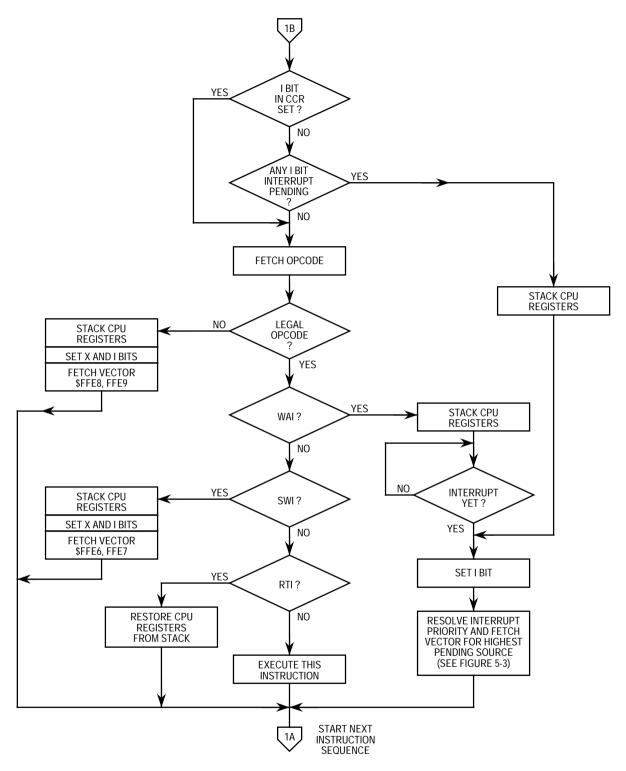

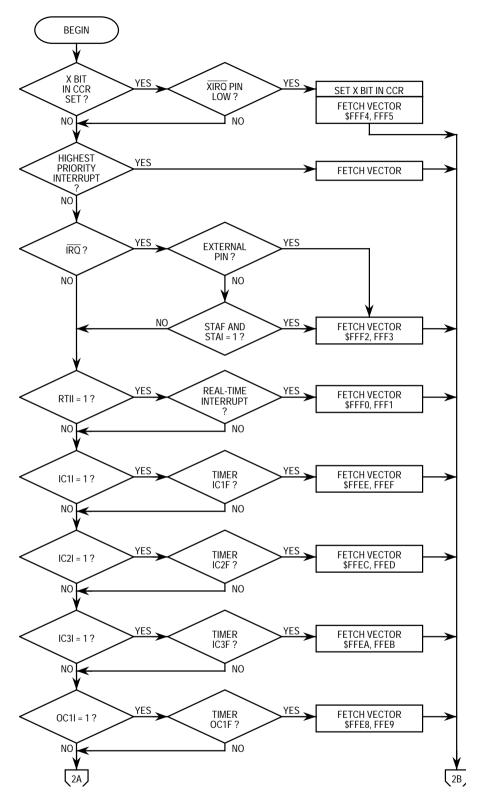

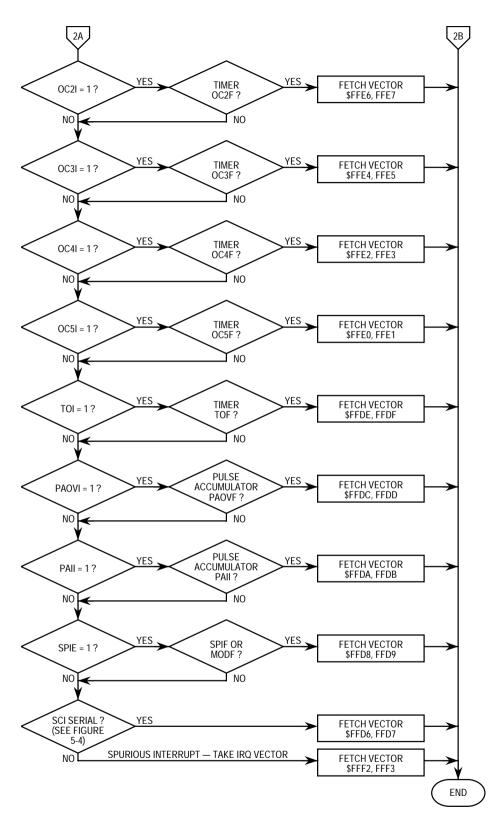

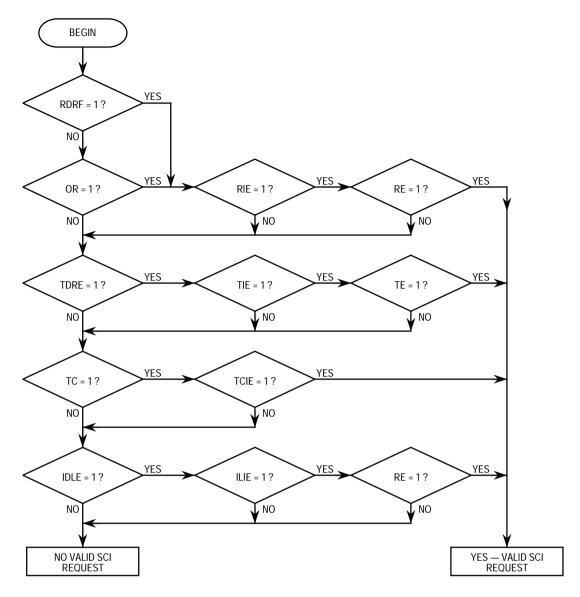

| Interrupt Process                              | 77<br> 78                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Non-Maskable Interrupts                        | 86<br> 88                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| Maskable Interrupts                            | 90                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interrupt Request                              | 93                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| Interrupts from Internal Peripheral Subsystems | 95<br> 95                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| •                                              | 197                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| Introduction                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

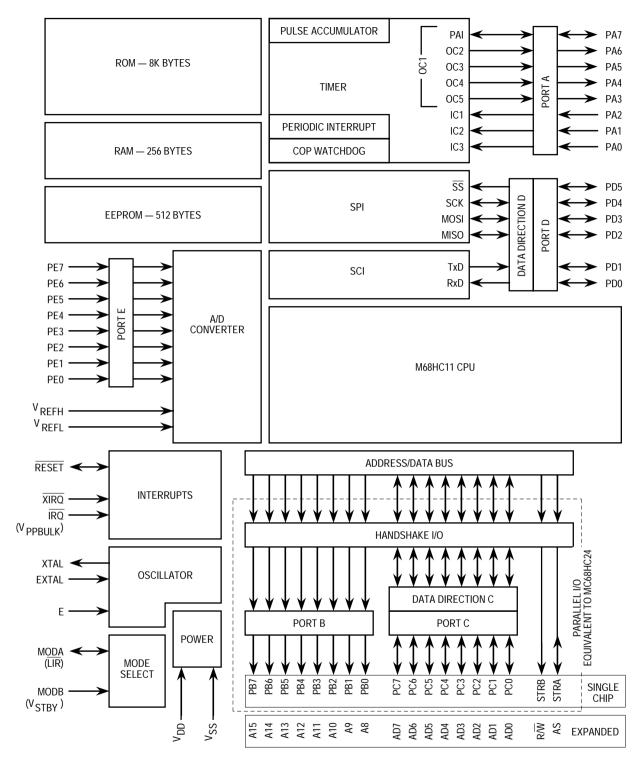

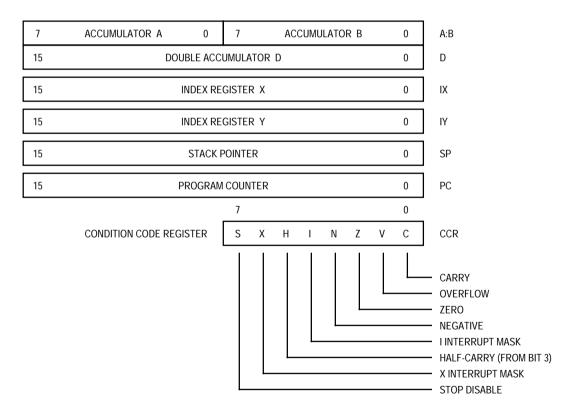

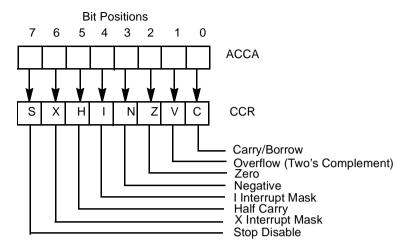

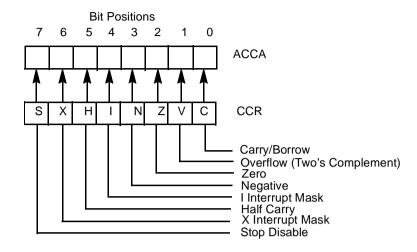

| Programmer's Model                             | 200<br>200<br>201<br>203                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                                                | Power-On Reset (POR) COP Watchdog Timer Reset Clock Monitor Reset External Reset Interrupt Process Interrupt Process Interrupt Recognition and Stacking Registers Selecting Interrupt Vectors Return from Interrupt Non-Maskable Interrupts Non-Maskable Interrupt Request (XIRQ) Illegal Opcode Fetch Software Interrupt.  Maskable Interrupts I Bit in the Condition Code Register Special Considerations for I-Bit-Related Instructions Interrupt Request Selecting Edge Triggering or Level Triggering Sharing Vector with Handshake I/O Interrupts Interrupts from Internal Peripheral Subsystems Inhibiting Individual Sources Clearing Interrupt Status Flag Bits Automatic Clearing Mechanisms on Some Flags.  Section 6. Central Processor Unit (CPU) Contents Introduction Programmer's Model Accumulators (A, B, and D) Index Registers (X and Y) Stack Pointer (SP) Program Counter (PC) |

### **Table of Contents**

| 6.4     | Addressing Modes                                   | 206  |

|---------|----------------------------------------------------|------|

| 6.4.1   | Immediate (IMM)                                    | 206  |

| 6.4.2   | Extended (EXT)                                     | 208  |

| 6.4.3   | Direct (DIR)                                       | 208  |

| 6.4.4   | Indexed (INDX and INDY)                            | 210  |

| 6.4.5   | Inherent (INH)                                     | 211  |

| 6.4.6   | Relative (REL)                                     | 212  |

| 6.5     | M68HC11 Instruction Set                            | 213  |

| 6.5.1   | Accumulator and Memory Instructions                | 214  |

| 6.5.1.1 | Loads, Stores, and Transfers                       | 215  |

| 6.5.1.2 | Arithmetic Operations                              | 216  |

| 6.5.1.3 | Multiply and Divide                                | 217  |

| 6.5.1.4 | Logical Operations                                 | 218  |

| 6.5.1.5 | Data Testing and Bit Manipulation                  | 219  |

| 6.5.1.6 | Shifts and Rotates                                 | 220  |

| 6.5.2   | Stack and Index Register Instructions              | 221  |

| 6.5.3   | Condition Code Register Instructions               | 223  |

| 6.5.4   | Program Control Instructions                       |      |

| 6.5.4.1 | Branches                                           | 225  |

| 6.5.4.2 | •                                                  | 226  |

| 6.5.4.3 |                                                    | 000  |

| 0544    | (BSR, JSR, and RTS)                                |      |

| 6.5.4.4 | 3 ( ) = , = ,                                      |      |

| 6.5.4.5 | Miscellaneous (NOP, STOP, and TEST)                | 227  |

|         | Section 7. Parallel Input/Output                   |      |

| 7.1     | Contents                                           | 229  |

| 7.2     | Introduction                                       | 230  |

| 7.3     | Parallel I/O Overview                              | 224  |

| 1.3     | raiallel I/O Overview                              | 23 I |

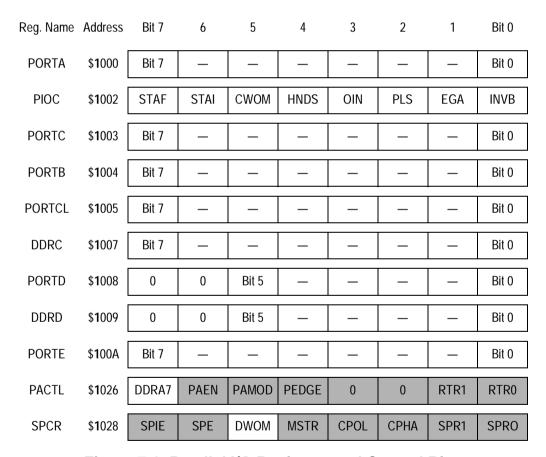

| 7.4     | Parallel I/O Register and Control Bit Explanations | 234  |

| 7.4.1   | Port Registers                                     | 236  |

| 7.4.2   | Data Direction Registers                           | 236  |

| 7.5     | Detailed I/O Pin Descriptions            | 238  |

|---------|------------------------------------------|------|

| 7.5.1   | Port A                                   | 238  |

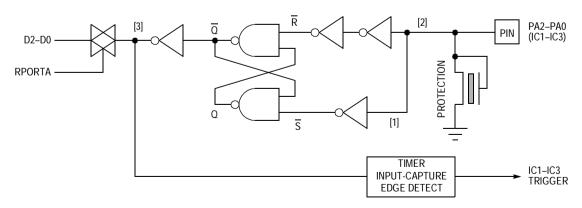

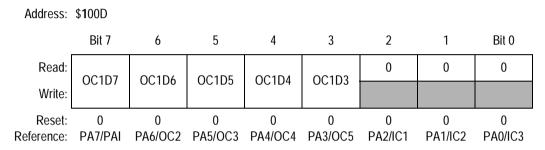

| 7.5.1.1 | PA2-PA0 (IC3-IC1) Pin Logic              | 238  |

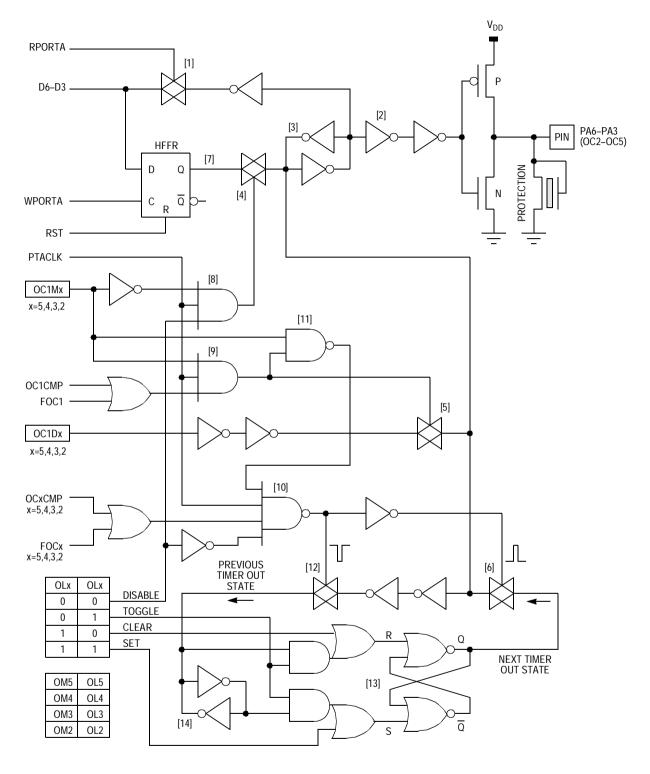

| 7.5.1.2 | PA6–PA3 (OC5–OC2) Pin Logic              | 240  |

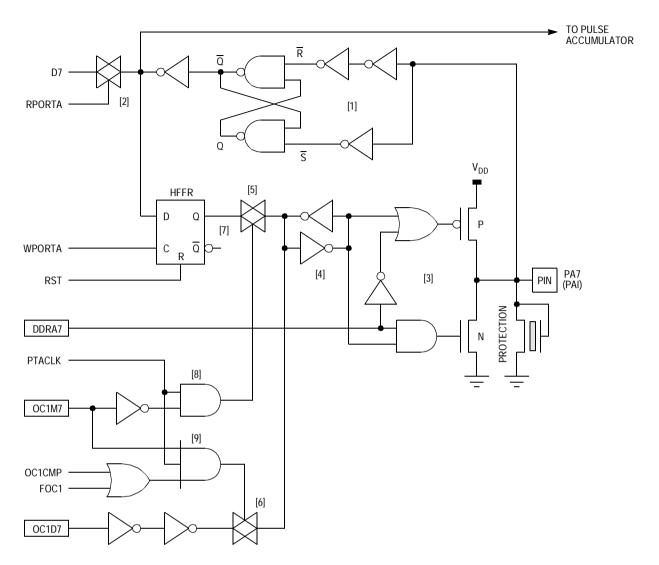

| 7.5.1.3 | PA7 (OC1 and PAI) Pin Logic              | 242  |

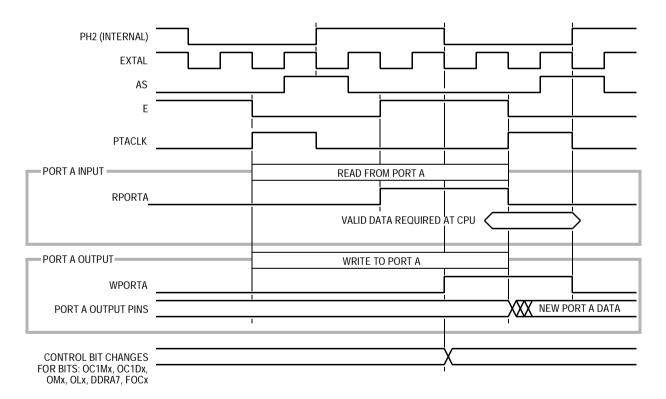

| 7.5.1.4 | 4 Port A Idealized Timing                | 244  |

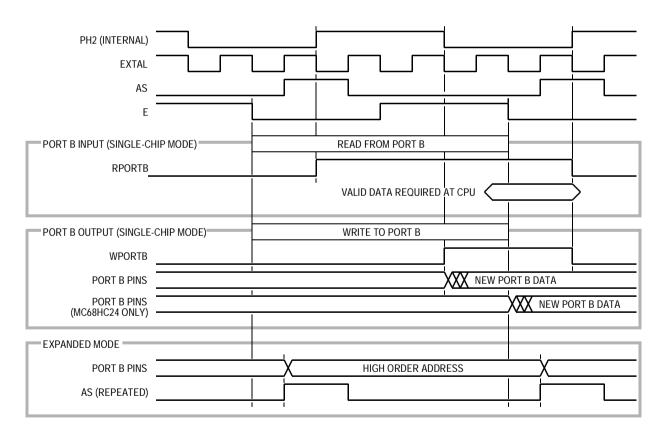

| 7.5.2   | Port B                                   | 245  |

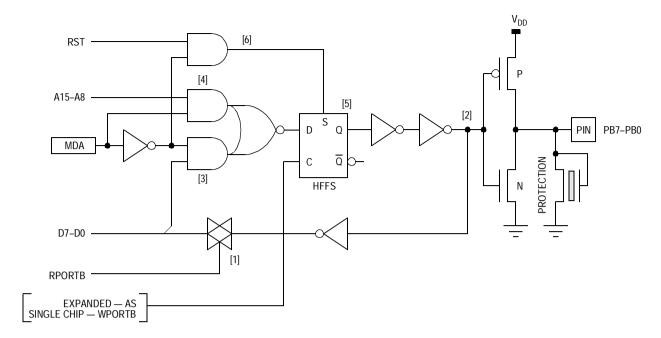

| 7.5.2.1 | Port B Pin Logic                         | 245  |

| 7.5.2.2 | Port B Idealized Timing                  | 246  |

| 7.5.2.3 | •                                        |      |

|         | on MC68HC24 PRU                          | 248  |

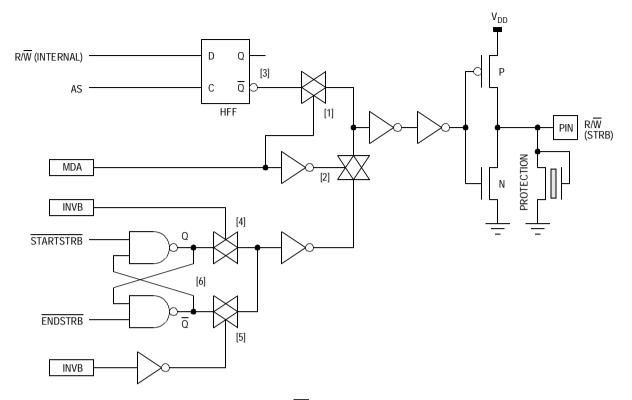

| 7.5.3   | R/W <u>(S</u> TRB) Pin                   | .248 |

| 7.5.3.1 | 1 R/W (STRB) Pin Logic                   | 248  |

| 7.5.3.2 | Special Considerations for STRB          |      |

|         | on MC68HC24 PRU                          | 250  |

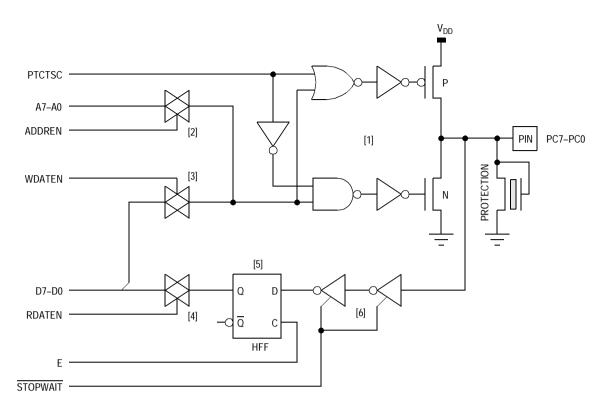

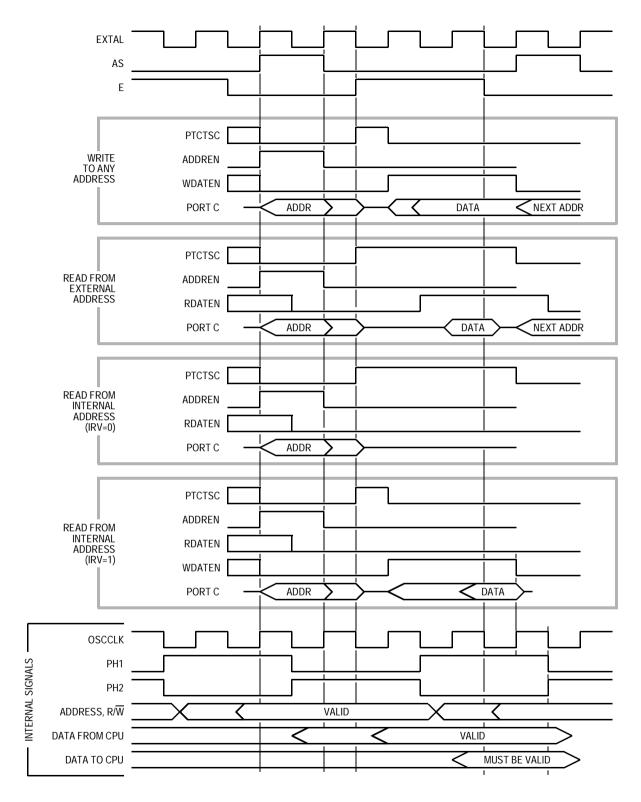

| 7.5.4   | Port C                                   |      |

| 7.5.4.1 | Port C Pin Logic for Expanded Modes      | .251 |

| 7.5.4.2 | •                                        |      |

|         | Expanded Mode Timing                     | 252  |

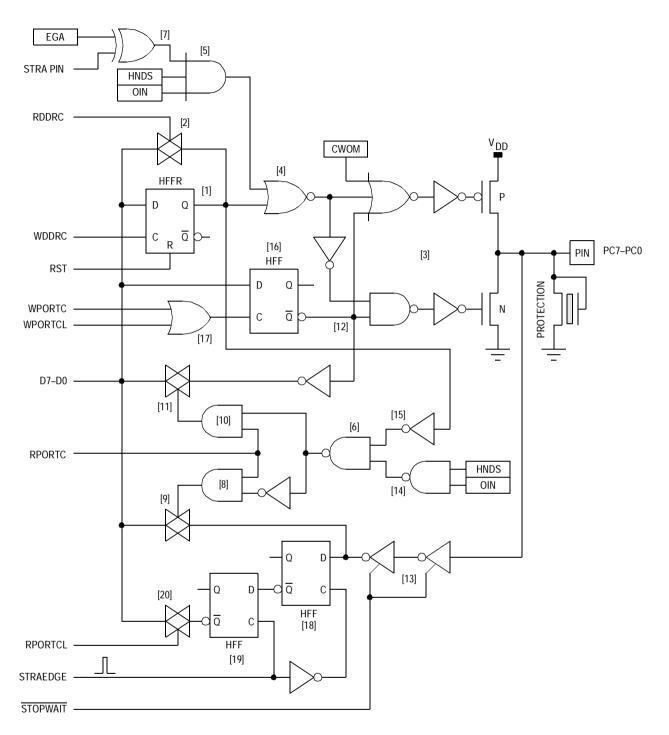

| 7.5.4.3 | Port C Single-Chip Mode Pin Logic        | 253  |

| 7.5.4.4 | Port C Idealized Single-Chip Mode Timing | 257  |

| 7.5.4.5 | Special Considerations for Port C        |      |

|         | on MC68HC24 PRU                          | 259  |

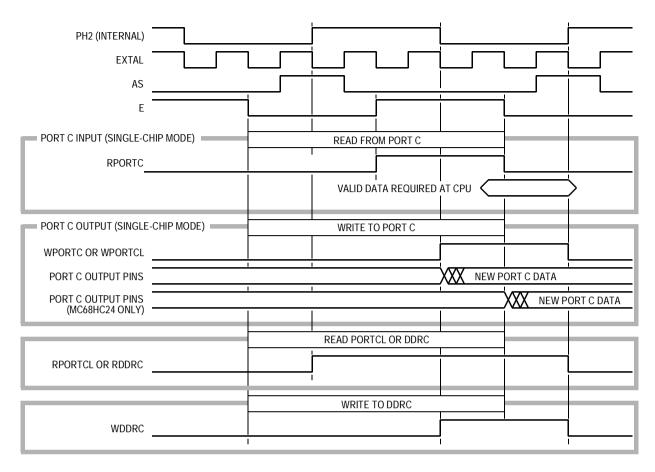

| 7.5.5   | AS (STRA) Pin                            | 259  |

| 7.5.5.1 | 1 AS (STRA) Pin Logic                    | 259  |

| 7.5.5.2 | ·                                        |      |

|         | on MC68HC24 PRU                          | 261  |

| 7.5.6   | Port D                                   | 261  |

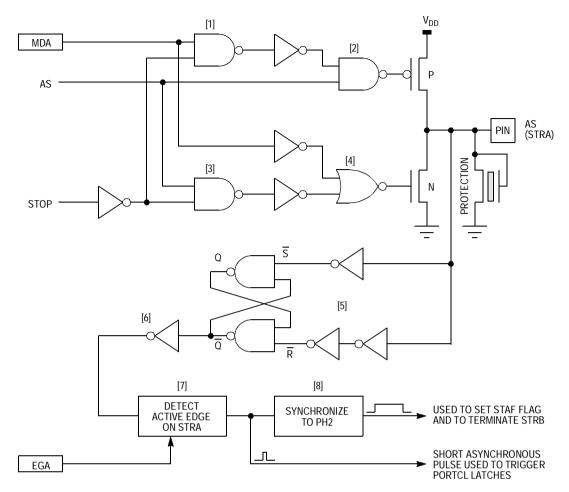

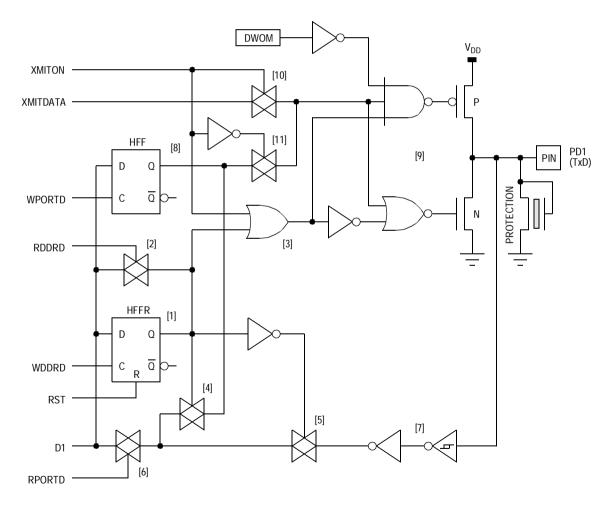

| 7.5.6.1 | PD0 (RxD) Pin Logic                      | 262  |

| 7.5.6.2 | PD1 (TxD) Pin Logic                      | 264  |

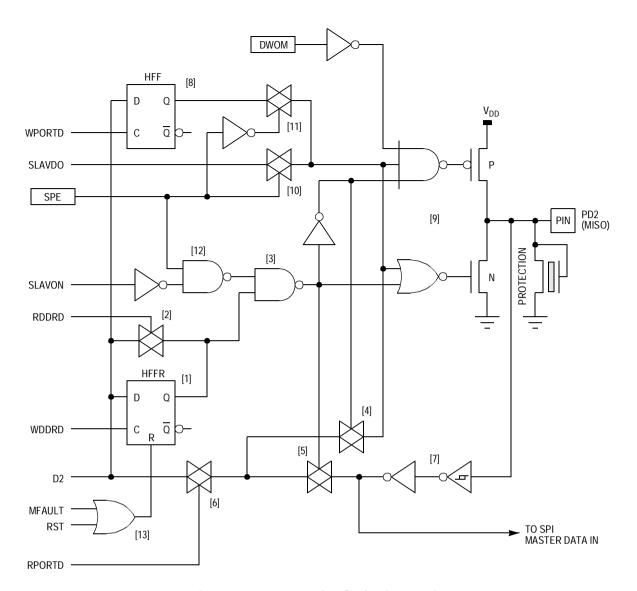

| 7.5.6.3 | PD2 (MISO) Pin Logic                     | 266  |

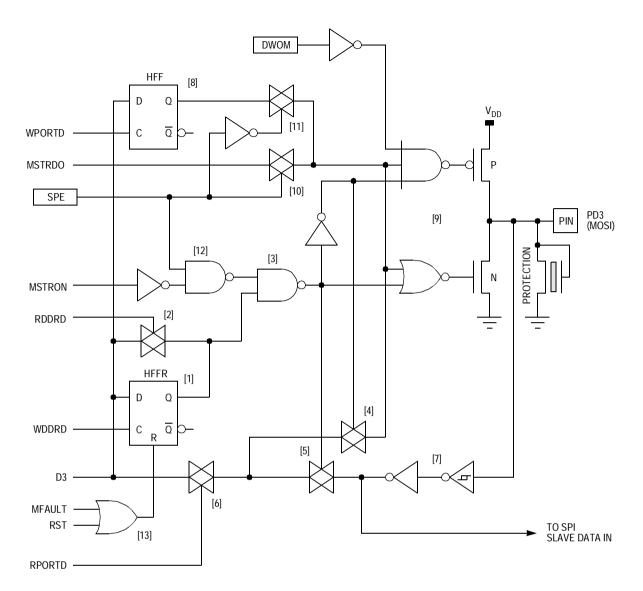

| 7.5.6.4 | 4 PD3 (MOSI) Pin Logic                   | 269  |

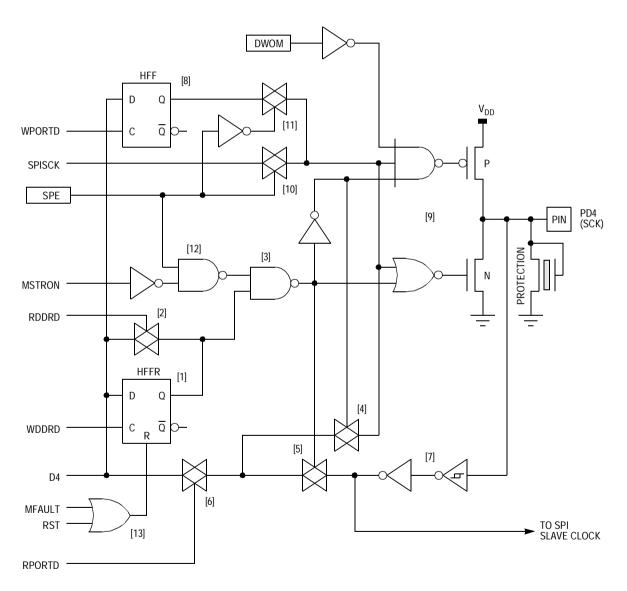

| 7.5.6.5 | 5 PD4 ( <u>SC</u> K) Pin Logic           | 272  |

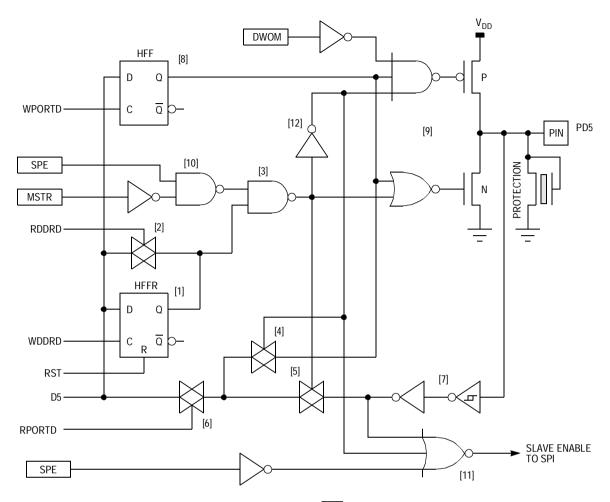

| 7.5.6.6 | PD5 (SS) Pin Logic                       | 274  |

| 7.5.6.7 | 7 Idealized Port D Timing                | 277  |

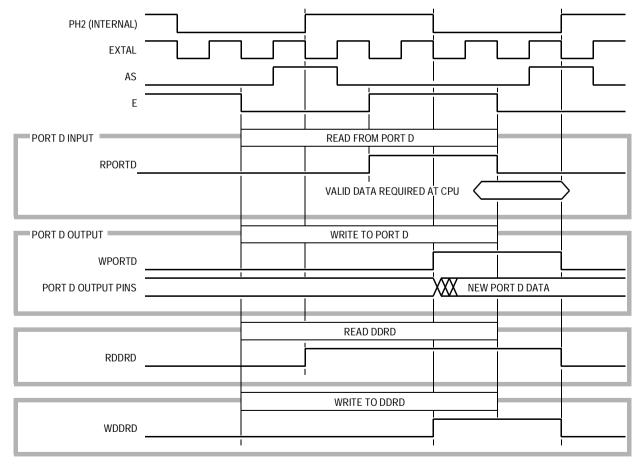

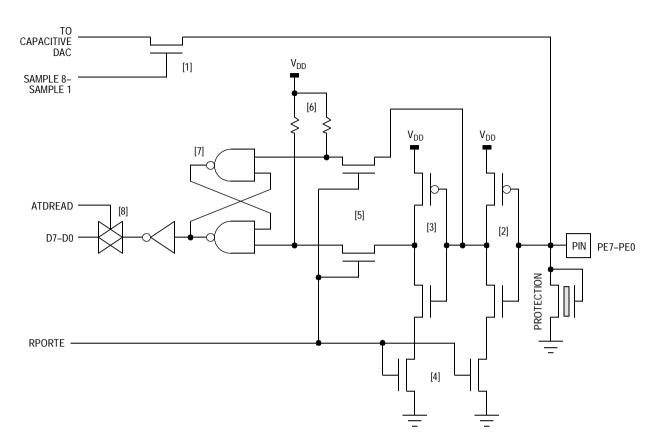

| 7.5.7   | Port E                                   | 278  |

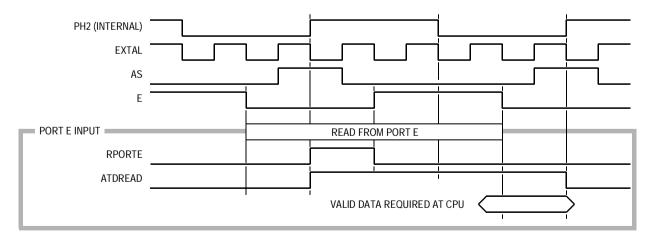

| 7.5.7.1 | Port E Pin Logic                         | 278  |

| 7.5.7.2 | Idealized Port E Timing                  | 280  |

**Table of Contents**

| 7.6    | Handshake I/O Subsystem                                                                            | 281         |

|--------|----------------------------------------------------------------------------------------------------|-------------|

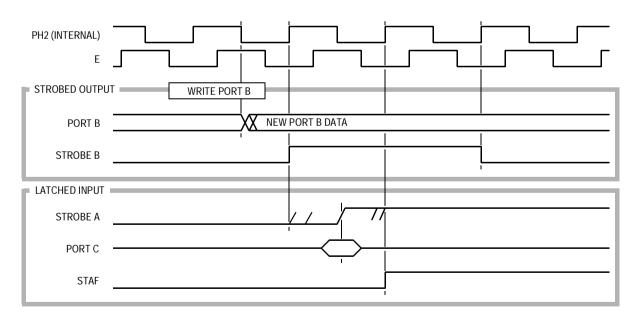

| 7.6.1  | Simple Strobe Mode                                                                                 |             |

| 7.6.1. |                                                                                                    |             |

| 7.6.1. | 2 Port C Simple Latching Input                                                                     | 283         |

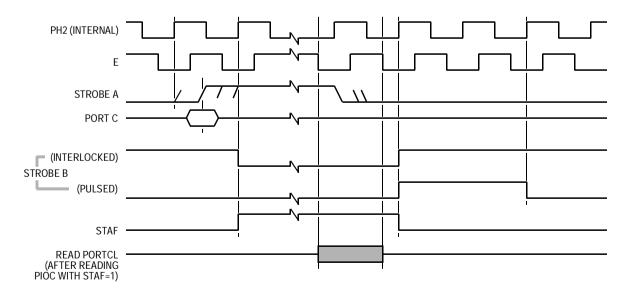

| 7.6.2  | Full-Input Handshake Mode                                                                          | 283         |

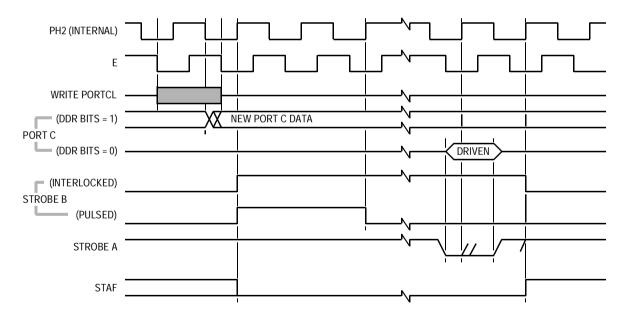

| 7.6.3  | Full-Output Handshake Mode                                                                         |             |

| 7.6.3. | Normal Output Handshake                                                                            | 286         |

| 7.6.3. | 2 Three-State Variation of Output Handshake                                                        | 286         |

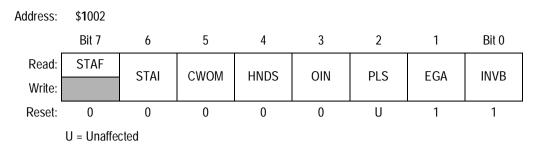

| 7.6.4  | Parallel I/O Control Register (PIOC)                                                               | 286         |

| 7.6.5  | Non-Handshake Uses of STRA and STRB Pins                                                           | 290         |

| S      | ection 8. Synchronous Serial Peripheral Interface                                                  |             |

|        | ·                                                                                                  |             |

| 8.1    | Contents                                                                                           | 291         |

| 8.2    | Introduction                                                                                       | 292         |

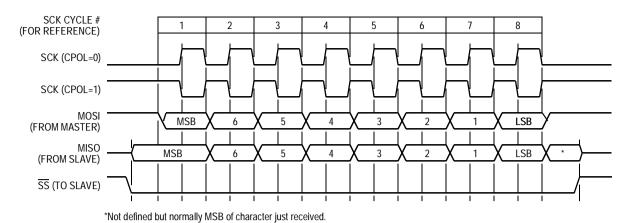

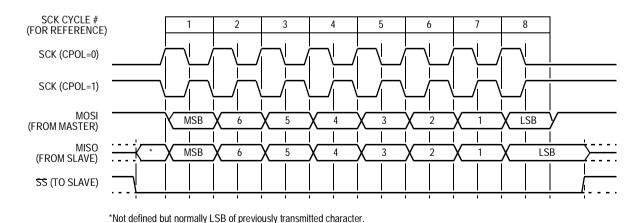

| 8.3    | SPI Transfer Formats                                                                               | 293         |

| 8.3.1  | SPI Clock Phase and Polarity Controls                                                              |             |

| 8.3.2  | CPHA Equals Zero Transfer Format                                                                   | 293         |

| 8.3.3  | CPHA Equals One Transfer Format                                                                    | 294         |

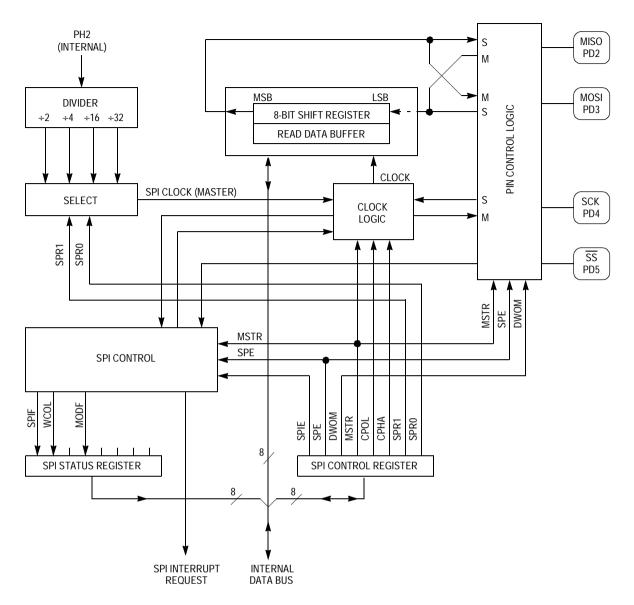

| 8.4    | SPI Block Diagram                                                                                  | 295         |

| 8.5    | SPI Pin Signals                                                                                    | 295         |

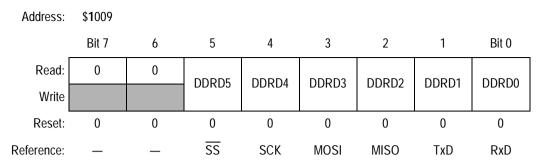

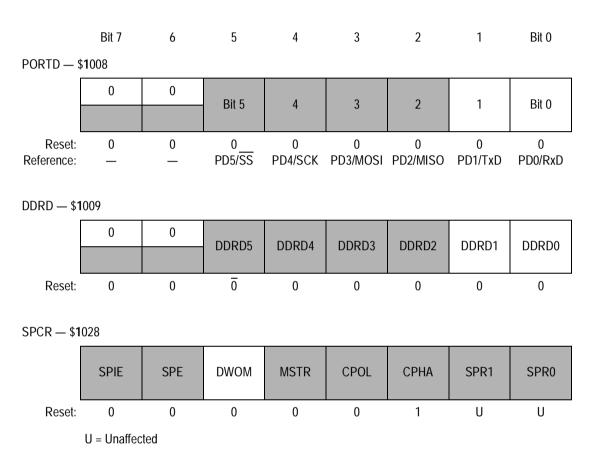

| 8.6    | SPI Registers                                                                                      | 298         |

| 8.6.1  | Port D Data Direction Control Register (DDRD)                                                      |             |

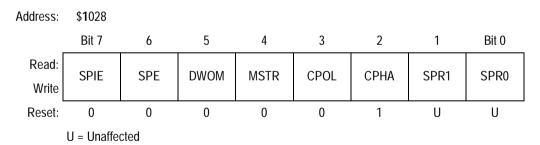

| 8.6.2  | SPI Control Register (SPCR)                                                                        |             |

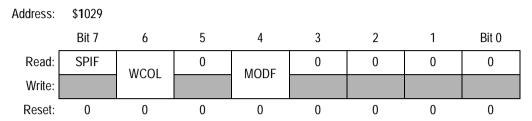

| 8.6.3  | SPI Status Register (SPSR)                                                                         |             |

|        |                                                                                                    |             |

| 8.7    | SPI System Errors                                                                                  |             |

| 8.7.1  | SPI Mode-Fault Error                                                                               |             |

| 8.7.2  | SPI Write-Collision Errors                                                                         | 304         |

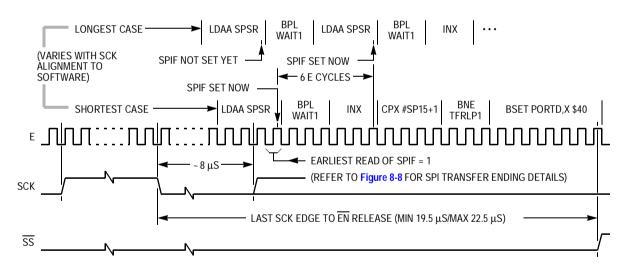

| 8.8    | Beginning and Ending SPI Transfers                                                                 | 305         |

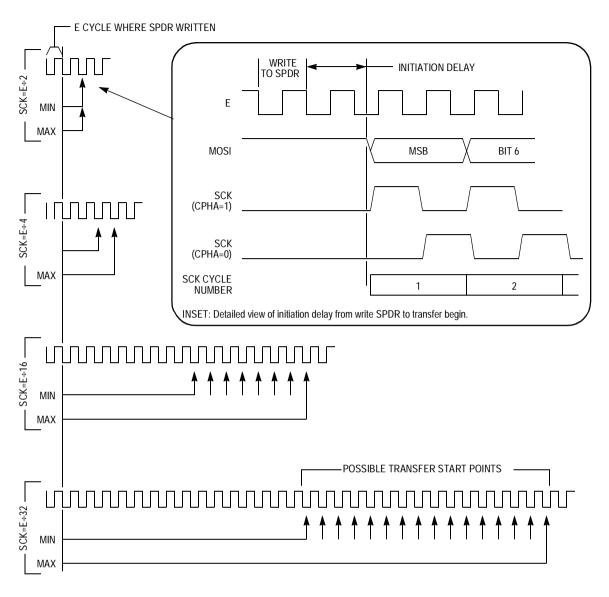

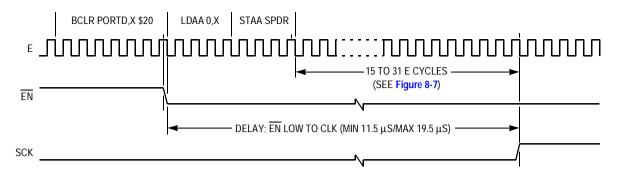

| 8.8.1  | Transfer Beginning Period (Initiation Delay)                                                       | 305         |

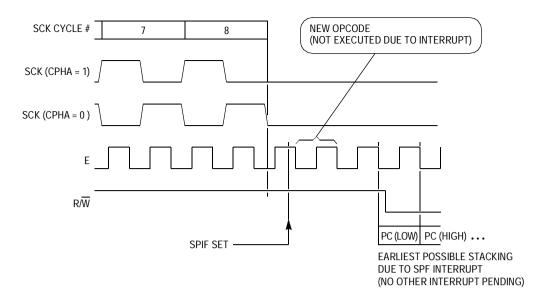

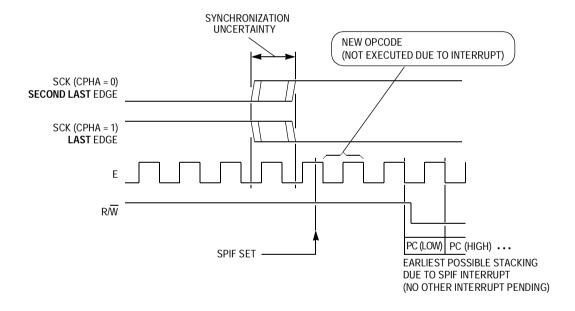

| 8.8.2  | Transfer Ending Period                                                                             | 306         |

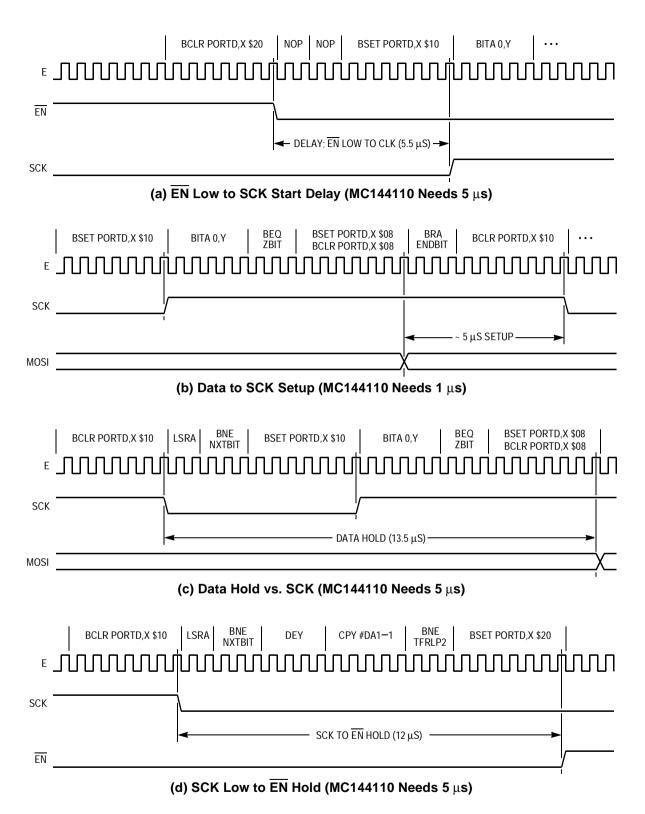

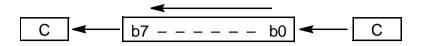

| 8.9    | Transfers to Peripherals with Odd Word Lengths                                                     | <b>3</b> 00 |

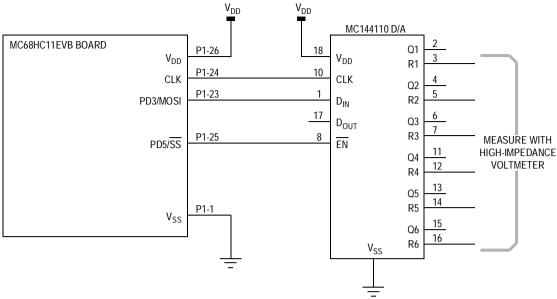

| 8.9.1  | Example 8-1: On-Chip SPI Driving an MC144110 D/A                                                   |             |

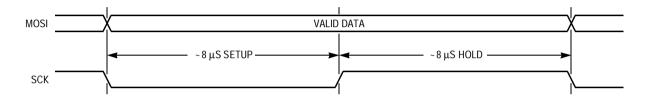

| 8.9.2  | Example 8-1. On-Chip SPI Driving an MC144110 D/A Example 8-2: Software SPI Driving an MC144110 D/A |             |

| 0.3.2  | Example 6-2. Sultware SET DIIVING AT MIC 144 FT0 D/A                                               | JII         |

# Section 9. Asynchronous Serial Communications Interface

| 9.1     | Contents                                  |

|---------|-------------------------------------------|

| 9.2     | Introduction                              |

| 9.3     | General Description                       |

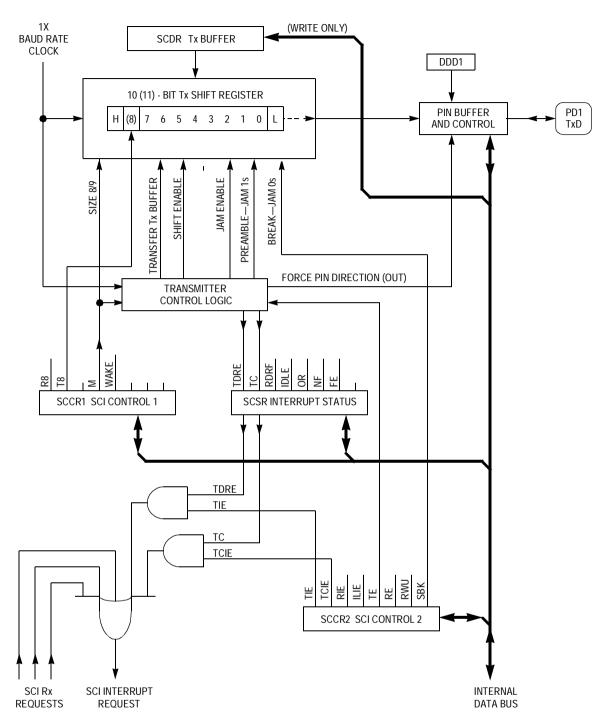

| 9.3.1   | Transmitter Block Diagram                 |

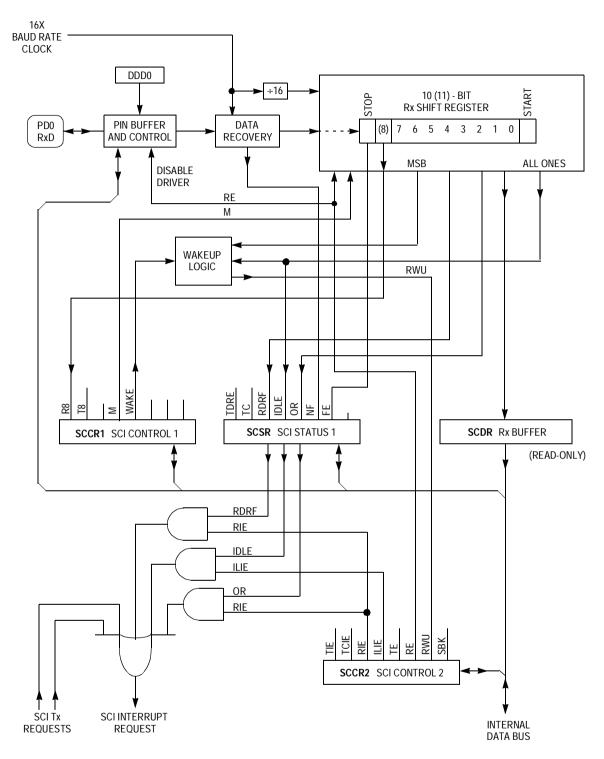

| 9.3.2   | Receiver Block Diagram321                 |

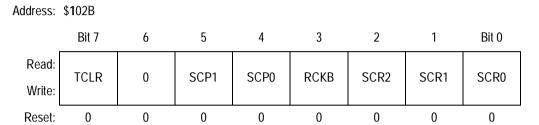

| 9.4     | SCI Registers and Control Bits323         |

| 9.4.1   | Port D Related Registers and Control Bits |

| 0.40    | (PORTD, DDRD, and SPCR)                   |

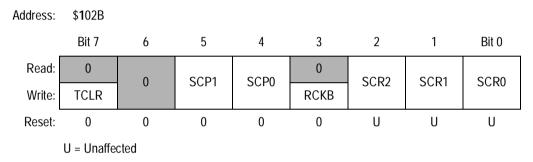

| 9.4.2   | Baud-Rate Control Register (BAUD)         |

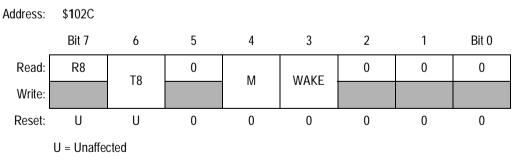

| 9.4.3   | SCI Control Register 1 (SCCR1)            |

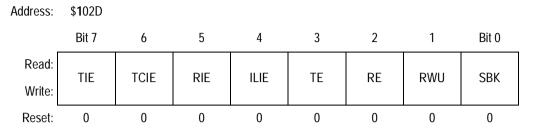

| 9.4.4   | SCI Control Register 2 (SCCR2)            |

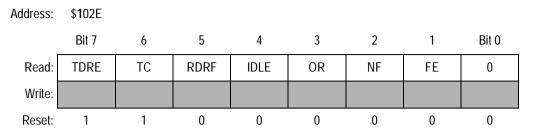

| 9.4.5   | SCI Status Register (SCSR)                |

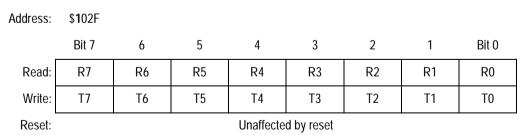

| 9.4.6   | SCI Data Register (SCDR)337               |

| 9.5     | SCI Transmitter338                        |

| 9.5.1   | 8- and 9-Bit Data Modes339                |

| 9.5.2   | Interrupts and Status Flags340            |

| 9.5.3   | Send Break341                             |

| 9.5.4   | Queued Idle Character341                  |

| 9.5.5   | Disabling the SCI Transmitter             |

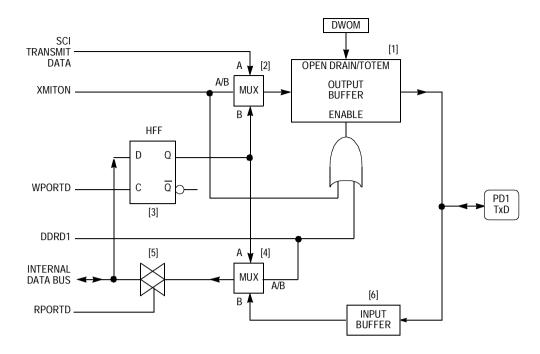

| 9.5.6   | TxD Pin Buffer Logic344                   |

| 9.6     | SCI Receiver                              |

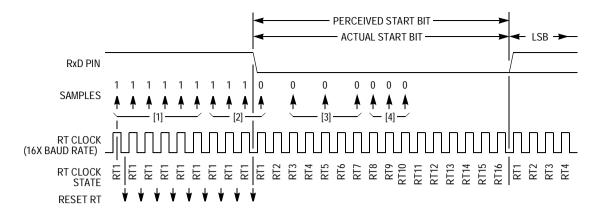

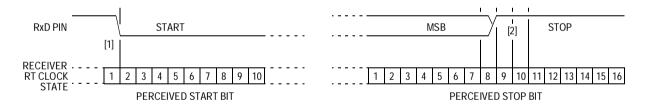

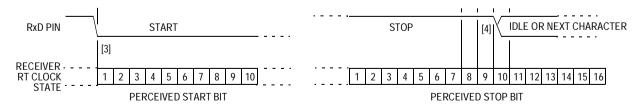

| 9.6.1   | Data Sampling Technique                   |

| 9.6.2   | Worst-Case Baud-Rate Mismatch             |

| 9.6.3   | Double-Buffered Operation355              |

| 9.6.4   | Receive Status Flags and Interrupts355    |

| 9.6.5   | Receiver Wakeup Operation                 |

| 9.6.5.  | •                                         |

| 9.6.5.2 | 2 Address-Mark Wakeup357                  |

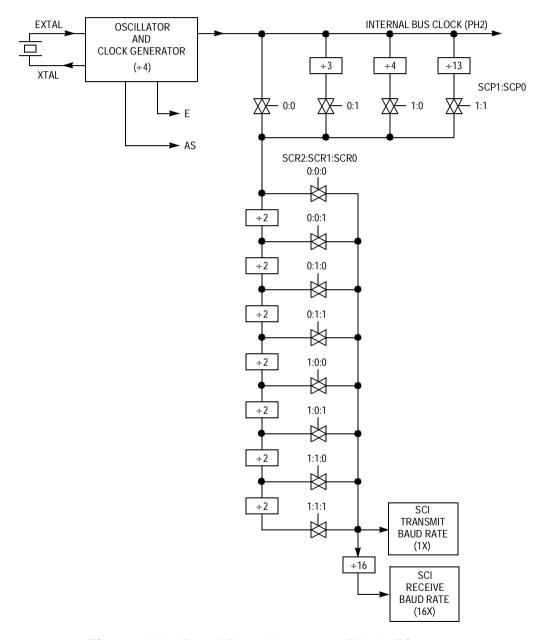

| 9.7     | Baud-Rate Generator                       |

| 9.7.1   | Timing Chain Block Diagram                |

| 9.7.2   | Baud Rates versus Crystal Frequency358    |

M68HC11 — Rev. 6.1 Reference Manual

**Table of Contents**

| 9.8     | SCI Timing Details                             |

|---------|------------------------------------------------|

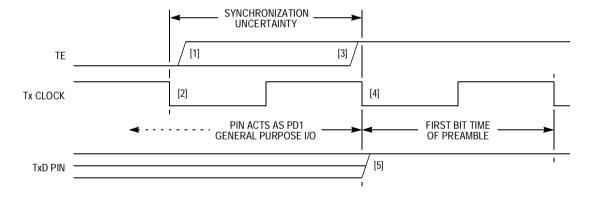

| 9.8.1   | Operation as Transmitter Is Enabled            |

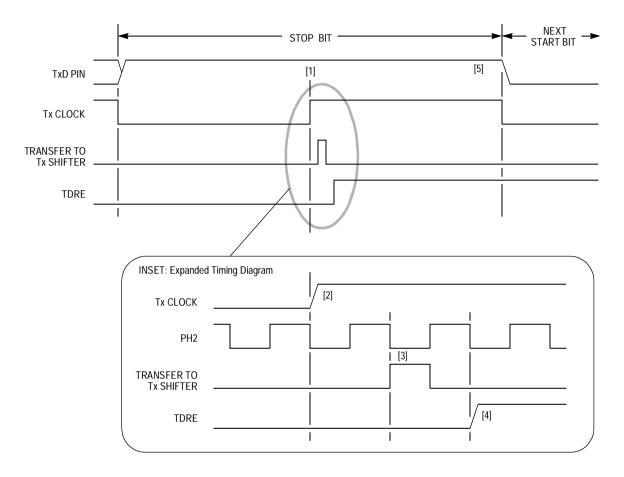

| 9.8.2   | TDRE and Transfers from SCDR                   |

|         | to Transmit Shift Register                     |

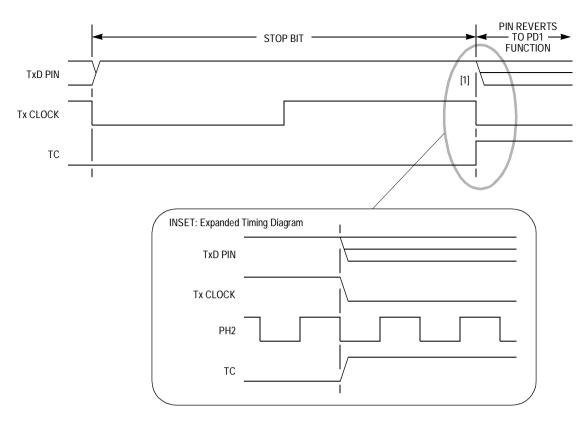

| 9.8.3   | TC versus Character Completion                 |

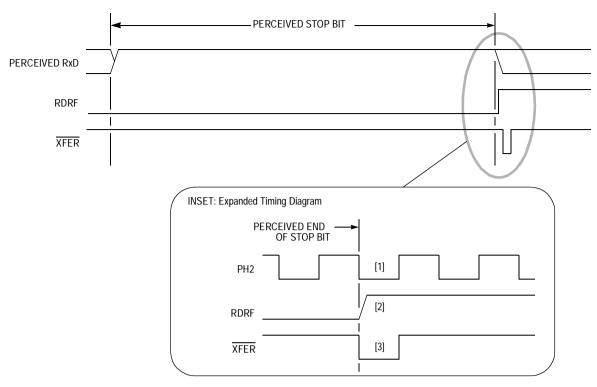

| 9.8.4   | RDRF Flag Setting versus End                   |

|         | of a Received Character                        |

|         |                                                |

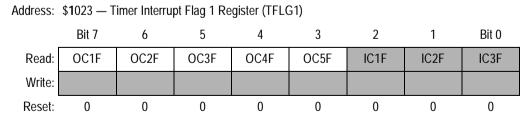

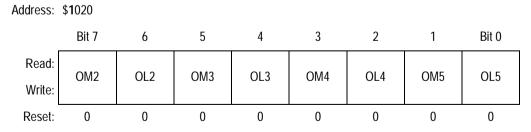

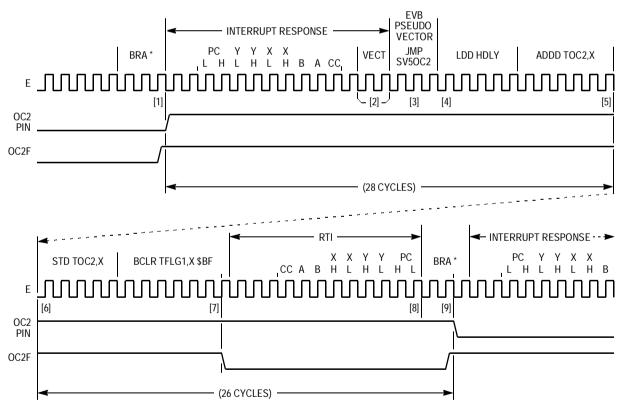

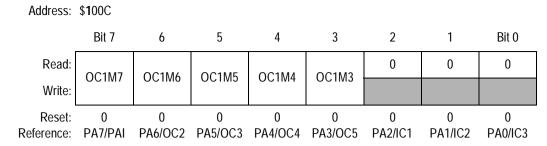

| 5       | Section 10. Main Timer and Real-Time Interrupt |

| 10.1    | Contents                                       |

| 10.2    | ntroduction368                                 |

| 10.3    | General Description                            |

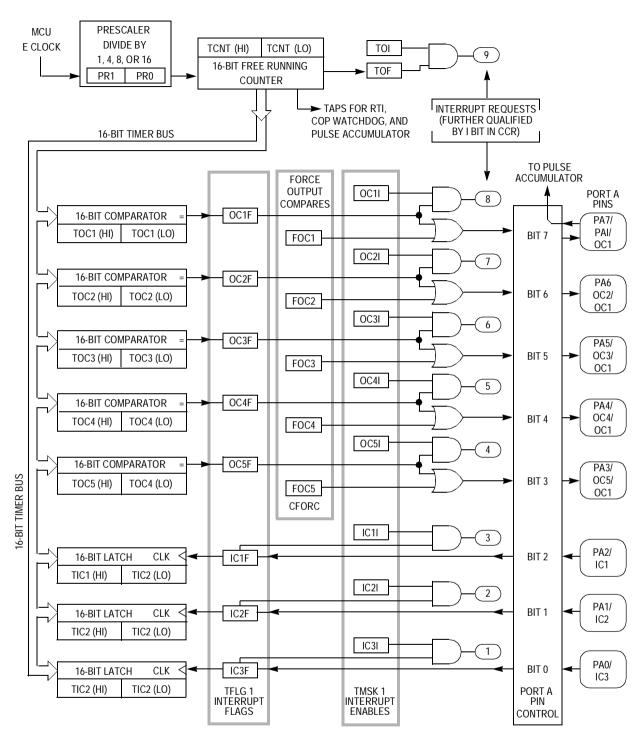

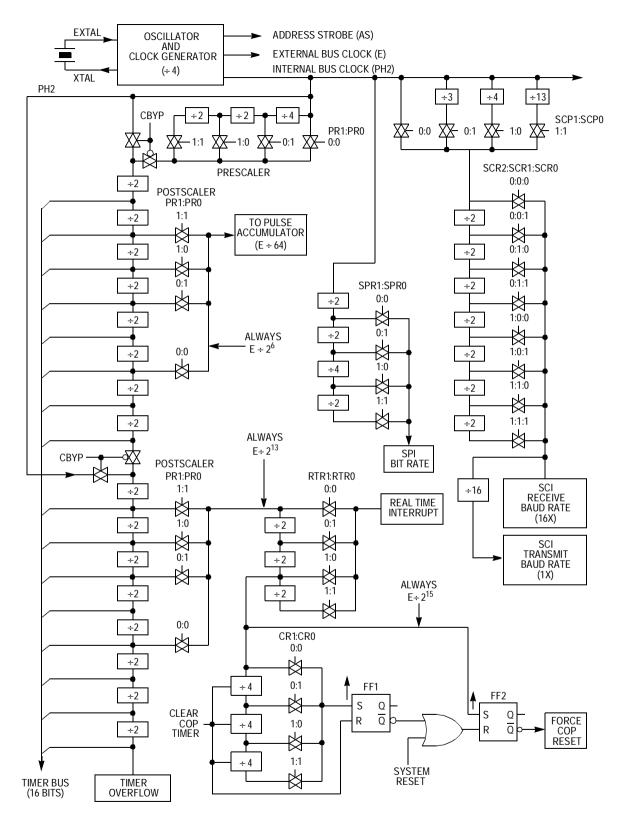

| 10.3.1  | Overall Timer Block Diagram                    |

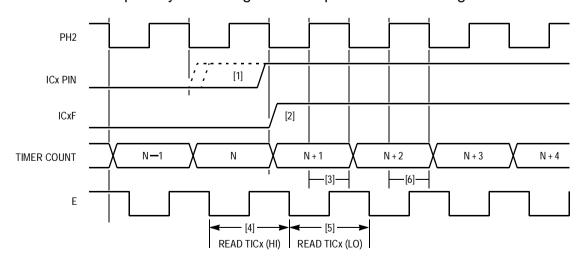

| 10.3.2  | Input-Capture Concept                          |

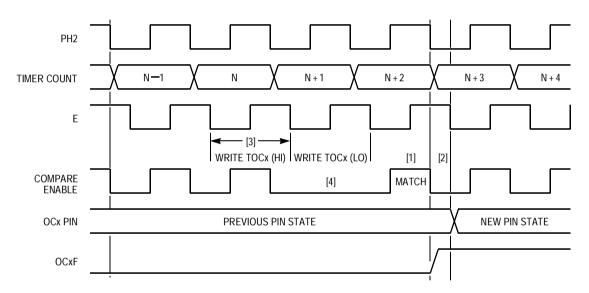

| 10.3.3  | Output-Compare Concept                         |

|         |                                                |

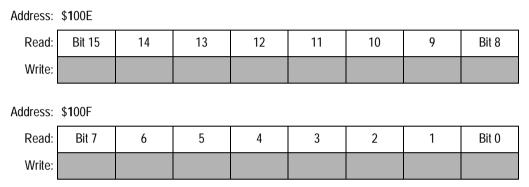

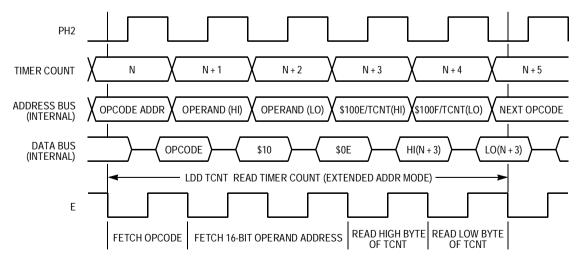

|         | Free-Running Counter and Prescaler             |

| 10.4.1  | Overall Clock Divider Structure375             |

| 10.4.1. |                                                |

| 10.4.1. |                                                |

| 10.4.1. | 71 (                                           |

| 10.4.2  | Real-Time Interrupt (RTI) Function382          |

| 10.4.3  | Computer Operating Properly (COP)              |

|         | Watchdog Function                              |

| 10.4.4  | Tips for Clearing Timer Flags387               |

|         | nput-Capture Functions                         |

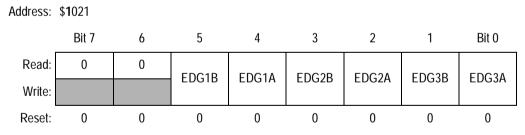

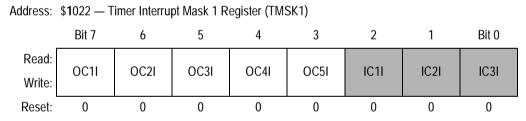

| 10.5.1  | Programmable Options392                        |

| 10.5.2  | Using Input Capture to Measure Period          |

|         | and Frequency393                               |

| 10.5.3  | Using Input Capture to Measure Pulse Width396  |

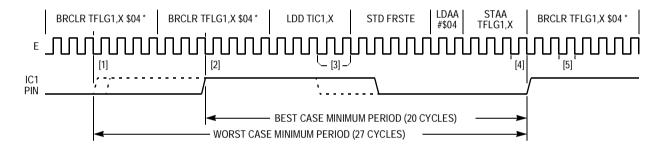

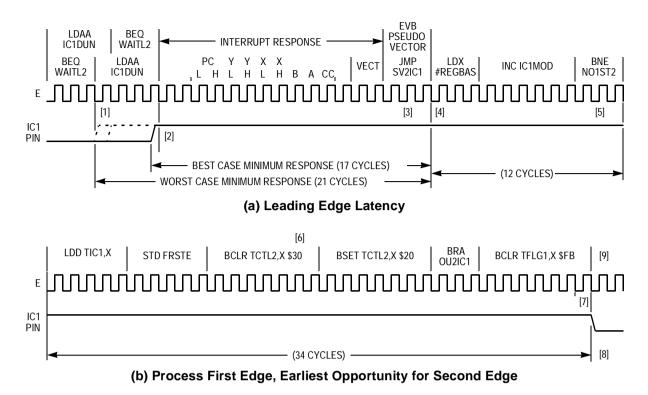

| 10.5.4  | Measuring Very Short Time Periods              |

| 10.5.5  | Measuring Long Time Periods                    |

|         | with Input Capture and Overflow401             |

| 10.5.6  | Establishing a Relationship between Software   |

|         | and an Event                                   |

| 10.5.7  | Other Uses for Input-Capture Pins406           |

|         |                                                |

| 10.6 Output-Compare Functions                              | 6  |

|------------------------------------------------------------|----|

| 10.6.1 Normal Input/Output Pin Control Using OC5–OC2 41    | 2  |

| 10.6.2 Advanced Input/Output Pin Control Using OC1         | 5  |

| 10.6.2.1 One Output Compare Controlling up to Five Pins 41 | 6  |

| 10.6.2.2 Two Output Compares Controlling One Pin41         | 7  |

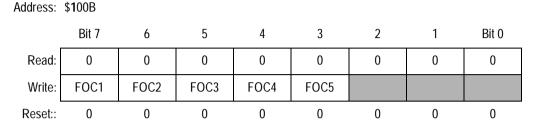

| 10.6.3 Forced Output Compares42                            | 0  |

| 10.7 Timing Details for the Main Timer System              | :1 |

| 10.8 Listing of Timer Examples                             | :5 |

| Section 11. Pulse Accumulator                              |    |

| 11.1 Contents                                              | .3 |

| 11.2 Introduction                                          | .3 |

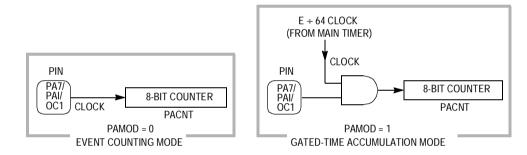

| 11.3 General Description                                   | 1  |

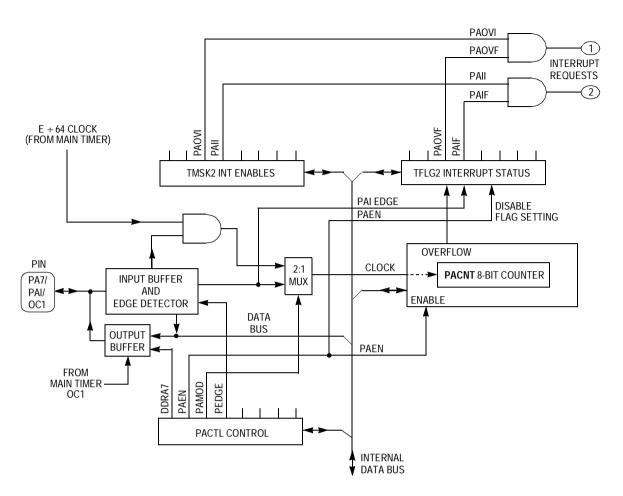

| 11.3.1 Pulse Accumulator Block Diagram                     |    |

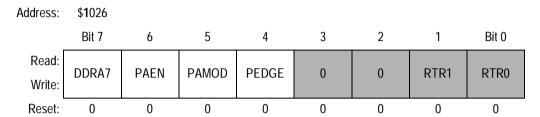

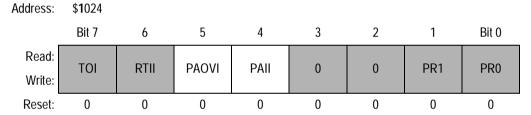

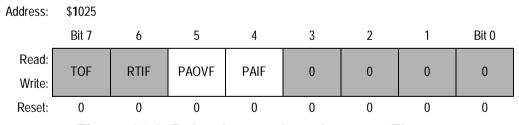

| 11.3.2 Pulse Accumulator Control and Status Registers      |    |

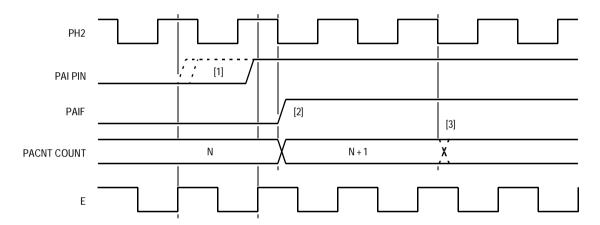

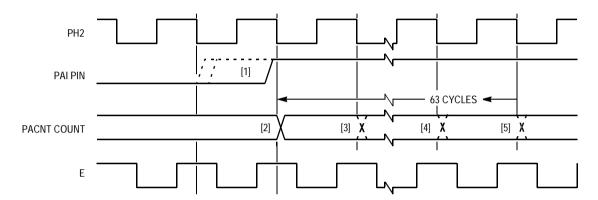

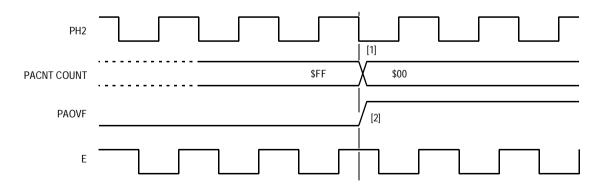

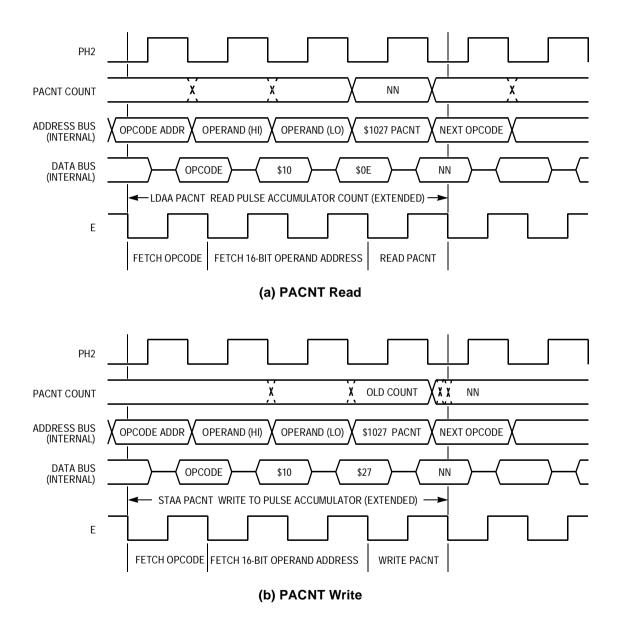

| 11.4 Event Counting Mode                                   | 0  |

| 11.4.1 Interrupting after N Events                         |    |

| 11.4.2 Counting More Than 256 Events                       |    |

| 11.5 Gated Time Accumulation Mode                          | 3  |

| 11.5.1 Measuring Times Longer Than the Range               |    |

| of the 8-Bit Counter                                       | 4  |

| 11.5.2 Configuring for Interrupt after a Specified Time    | 5  |

| 11.6 Other Uses for the PAI Pin                            | 5  |

| 11.7 Timing Details for the Pulse Accumulator45            | 5  |

| Section 12. Analog-to-Digital Converter System             |    |

| 12.1 Contents                                              | 9  |

| 12.2 Introduction                                          | 9  |

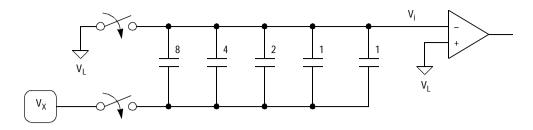

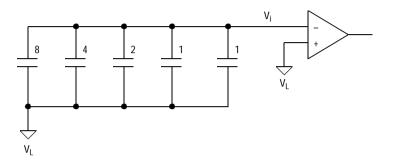

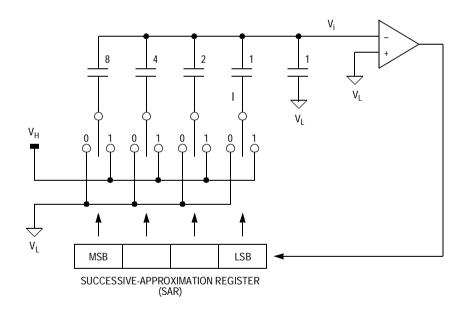

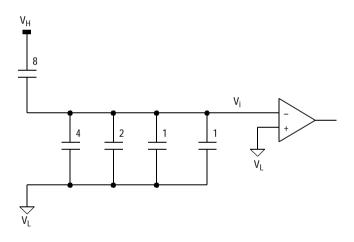

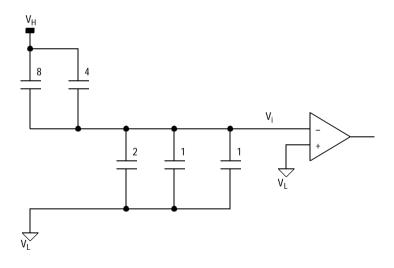

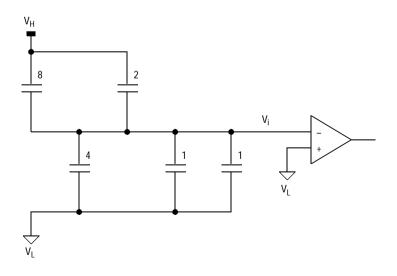

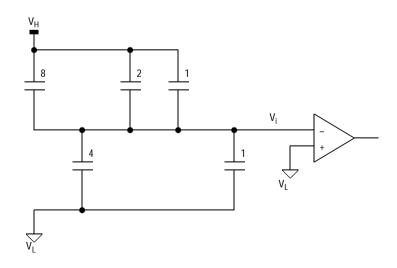

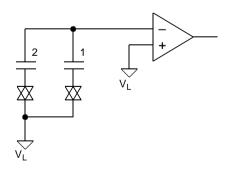

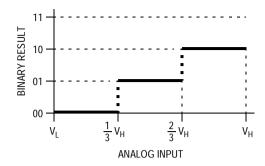

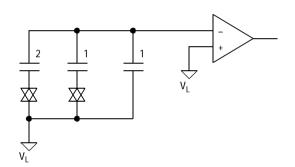

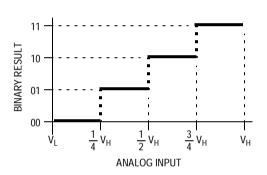

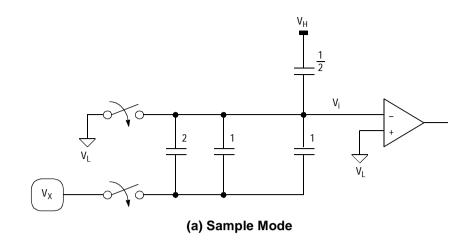

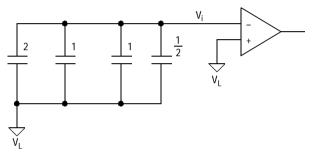

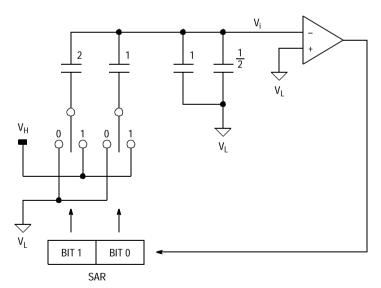

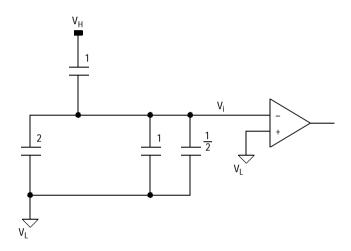

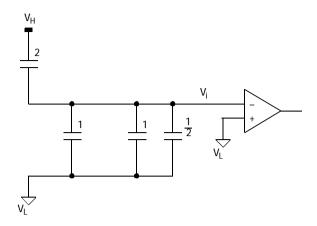

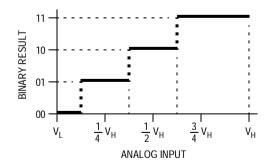

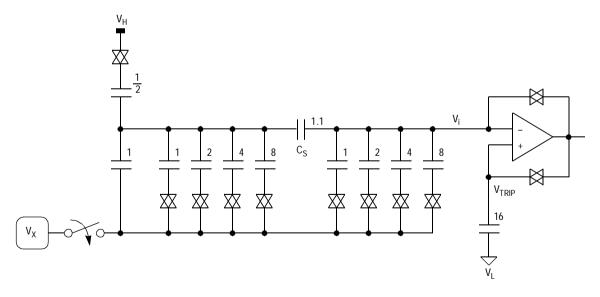

| 12.3 Charge-Redistribution A/D                             | 0  |

### **Table of Contents**

| 12.4   | A/D Converter Implementation on MC68HC11A8    | ′1         |

|--------|-----------------------------------------------|------------|

| 12.4.1 | MC68HC11A8 Successive-Approximation           |            |

|        | A/D Converter                                 | <b>7</b> 1 |

| 12.4.2 | 2 A/D Charge Pump and Resistor-Capacitor (RC) |            |

|        | Oscillator                                    | <b>7</b> 2 |

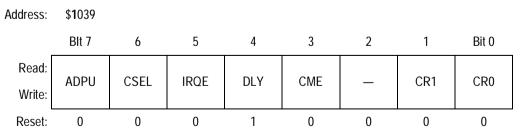

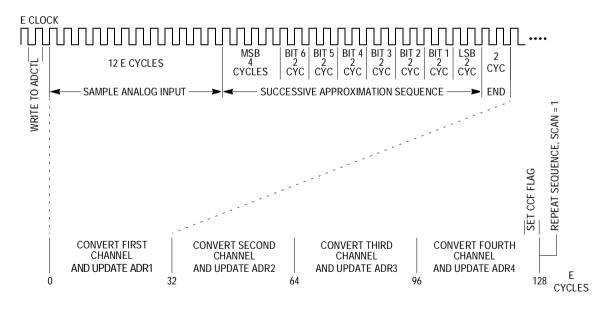

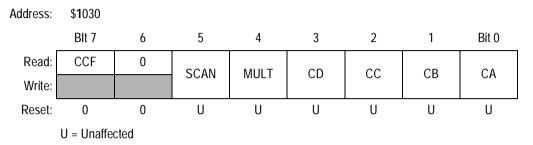

| 12.4.3 | MC68HC11A8 A/D System Control Logic           | <b>7</b> 4 |

| 12.4.4 |                                               |            |

| 12.4.5 |                                               |            |

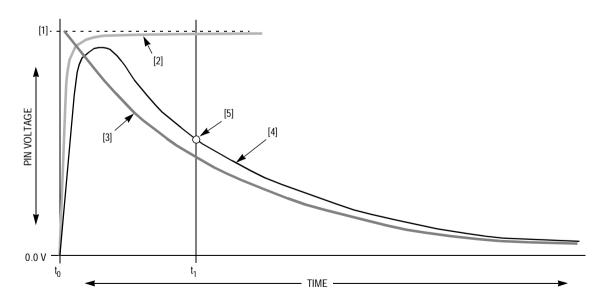

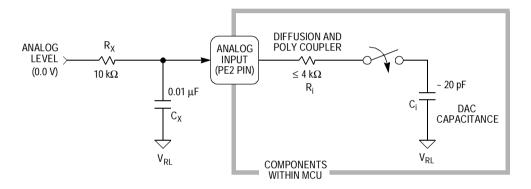

| 12.5   | A/D Pin Connection Considerations             | <b>'</b> 8 |

|        | Appendix A. Instruction Set Details           |            |

| A.1    | Contents                                      | 37         |

| A.2    | Introduction                                  | 37         |

| A.3    | Nomenclature                                  | 38         |

| A.4    | M68HC11 Instruction Set                       | <b>)</b> 1 |

|        | Appendix B. Bootloader Listings               |            |

|        | Bootloader Listings                           | )3         |

|        | Index                                         |            |

|        | Index 63                                      | 21         |

List of Figures

# **List of Figures**

| Figur | e Title                                          | Page |

|-------|--------------------------------------------------|------|

| 1-1   | Block Diagram                                    | 30   |

| 1-2   | M68HC11 Programmer's Model                       | 31   |

| 1-3   | Part Numbering                                   | 34   |

| 2-1   | MC68HC11A8 Pin Assignments                       | 38   |

| 2-2   | MC68HC11D3/711D3 Pin Assignments                 | 39   |

| 2-3   | MC68HC11E9/711E9 Pin Assignments (52-Pin PLCC)   | 41   |

| 2-4   | MC68HC811E2 Pin Assignments (48-Pin DIP)         | 42   |

| 2-5   | MC68HC11F1 Pin Assignments (68-Pin PLCC)         |      |

| 2-6   | MC68HC24 Pin Assignments                         |      |

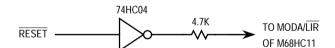

| 2-7   | Reduced I <sub>DD</sub> MODA/LIR Connections     | 48   |

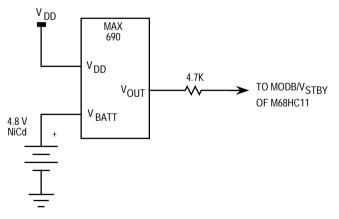

| 2-8   | RAM Standby MODB/V <sub>STBY</sub> Connections   |      |

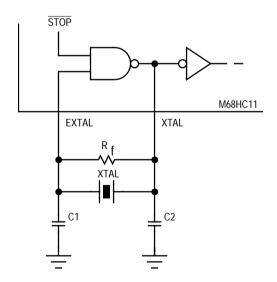

| 2-9   | High-Frequency Crystal Connections               | 51   |

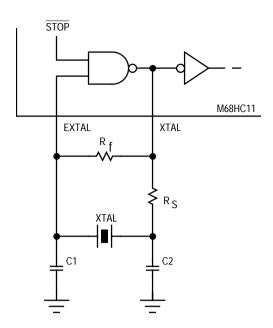

| 2-10  | Low-Frequency Crystal Connections                |      |

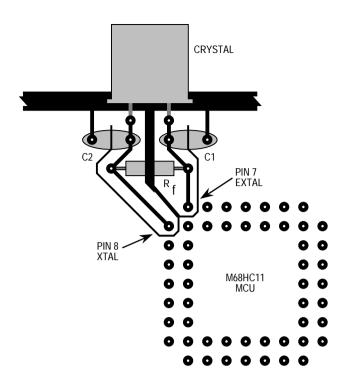

| 2-11  | Crystal Layout Example                           |      |

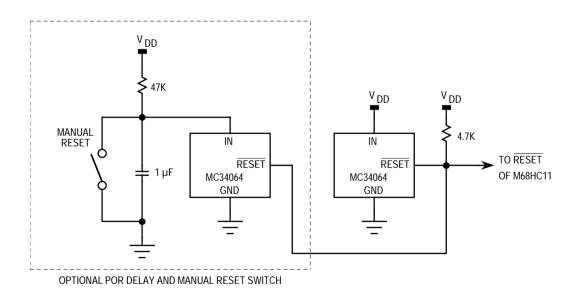

| 2-12  | Reset Circuit Example                            |      |

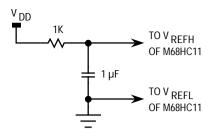

| 2-13  | Low-Pass Filter for A/D Reference Pins           |      |

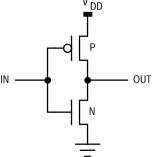

| 2-14  | CMOS Inverter                                    |      |

| 2-15  | Internal Circuitry — Digital Input-Only Pin      |      |

| 2-16  | Internal Circuitry — Analog Input-Only Pin       |      |

| 2-17  | Internal Circuitry — Digital I/O Pin             |      |

| 2-18  | Internal Circuitry — Input/Open-Drain-Output Pin |      |

| 2-19  | Internal Circuitry — Output-Only Pin             |      |

| 2-20  | Internal Circuitry — MODB/V <sub>STBY</sub> Pin  |      |

| 2-21  | Internal Circuitry — IRQ/V <sub>PPBULK</sub> Pin |      |

| 2-22  | Basic Expanded Mode Connections                  |      |

| 2-23  | Basic Single-Chip Mode Connections               | 80   |

M68HC11 — Rev. 6.1 Reference Manual

19

### List of Figures

| Figur | e Title                                              | Page |

|-------|------------------------------------------------------|------|

| 3-1   | Highest Priority I-Bit Interrupt                     |      |

|       | and Miscellaneous Register (HPRIO)                   | 88   |

| 3-2   | System Configuration Register (CONFIG)               | 91   |

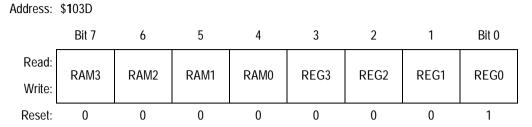

| 3-3   | RAM and I/O Mapping Register (INIT)                  | 95   |

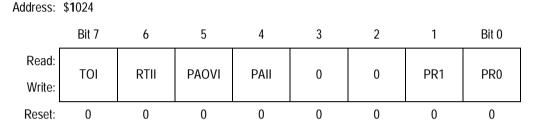

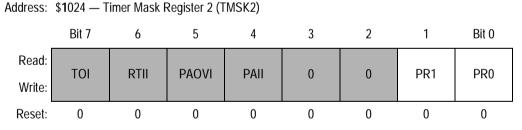

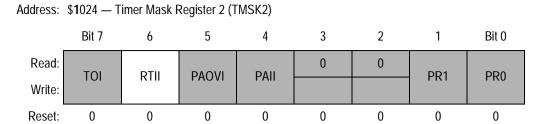

| 3-4   | Timer Mask Register 2 (TMSK2)                        | 98   |

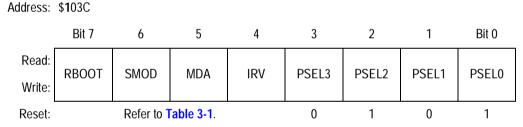

| 3-5   | System Configuration Option Register (OPTION)        | 99   |

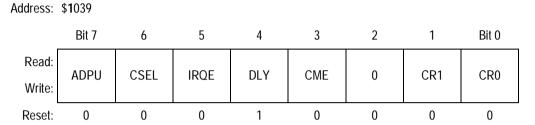

| 3-6   | Testing Functions Control Register (TEST1)           | 104  |

| 3-7   | Testing Functions Control Register (BAUD)            | 107  |

| 3-8   | Schematic for Figure 3-9                             | 117  |

| 3-9   | Program to Check/Change CONFIG                       | 119  |

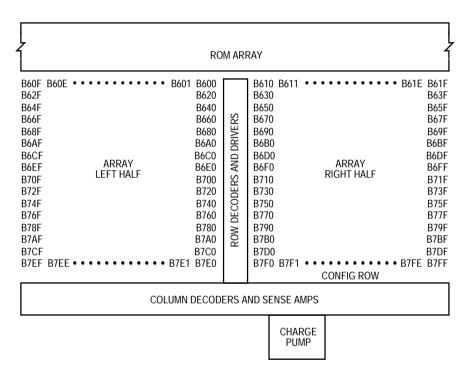

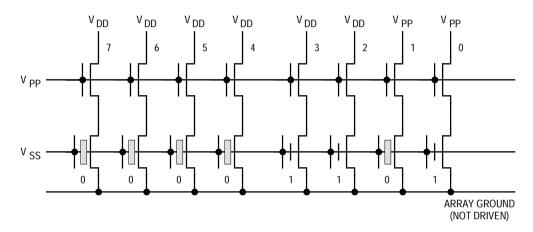

| 4-1   | Topological Arrangement of EEPROM Bytes (MC68HC11A8) | 128  |

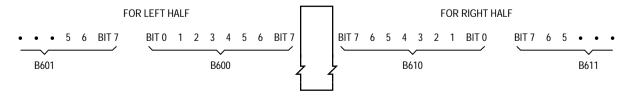

| 4-2   | Topological Arrangement of Bits in an EEPROM Byte    |      |

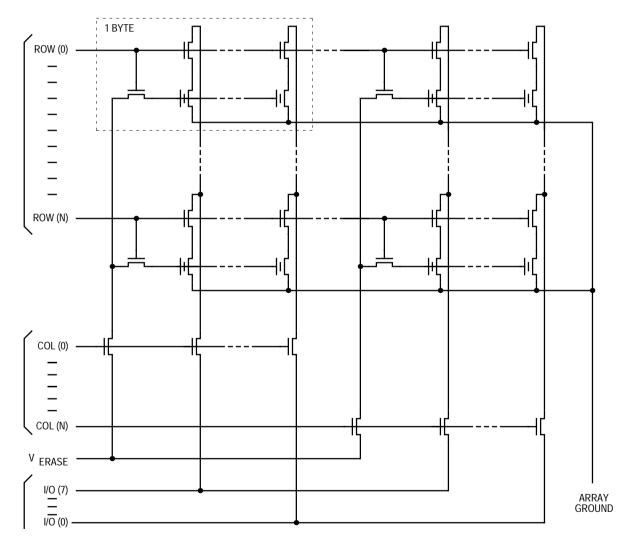

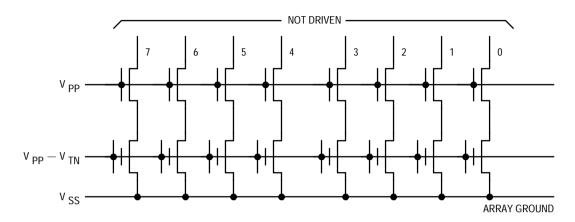

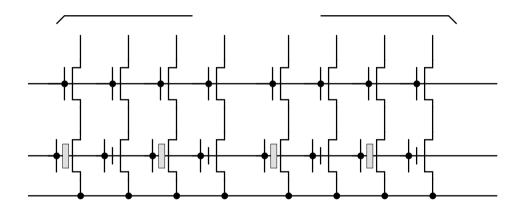

| 4-3   | Condensed Schematic of EEPROM Array                  |      |

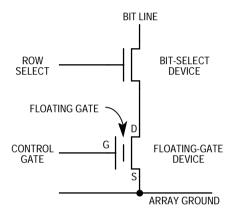

| 4-4   | EEPROM Cell Terminology                              |      |

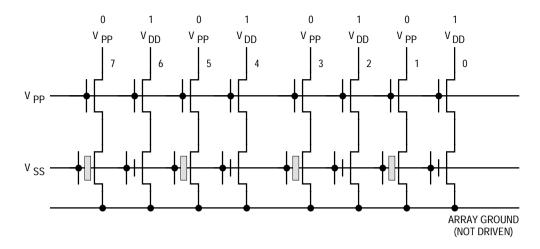

| 4-5   | Erasing an EEPROM Byte                               |      |

| 4-6   | Programming an EEPROM Byte                           | 132  |

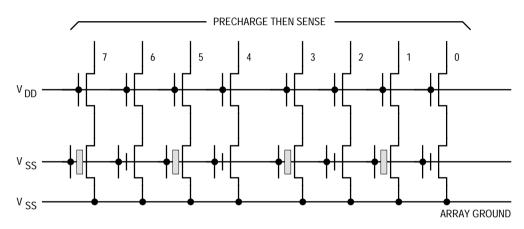

| 4-7   | Reading an EEPROM Byte                               |      |

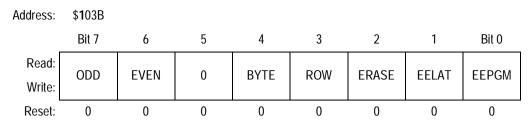

| 4-8   | EEPROM Programming Register (PPROG)                  |      |

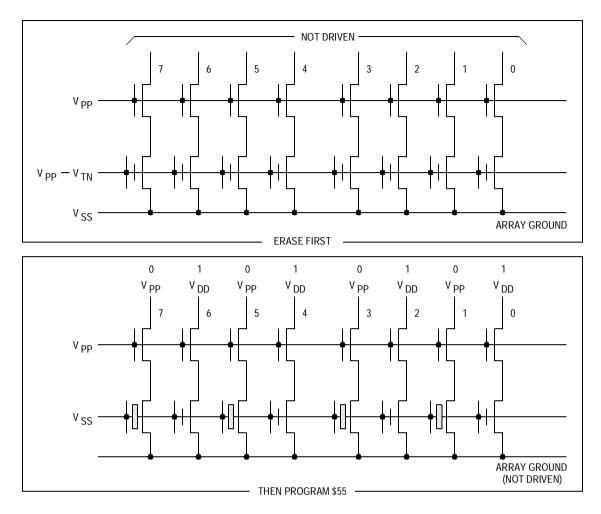

| 4-9   | Erase-Before-Write Programming Method                |      |

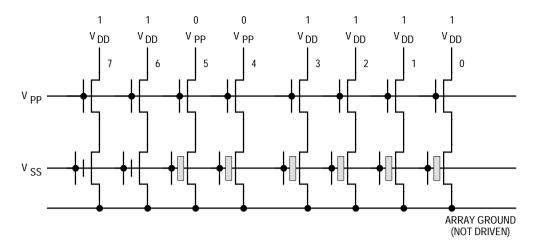

| 4-10  | Program-More-Zeros Programming Method                | 155  |

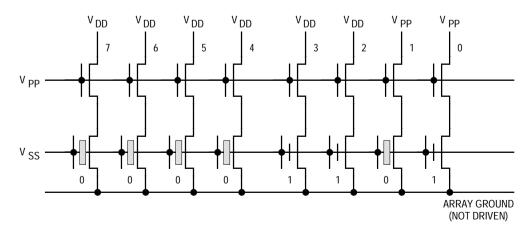

| 4-11  | Selective-Write Programming Method                   | 155  |

| 4-12  | Composite Programming Method                         | 156  |

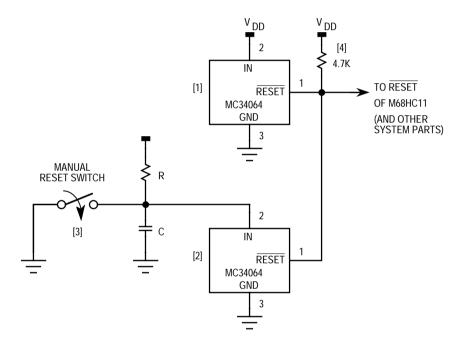

| 5-1   | Typical External Reset Circuit                       | 175  |

| 5-2   | Highest Priority I-Bit Interrupt                     |      |

|       | and Miscellaneous Register (HPRIO)                   | 179  |

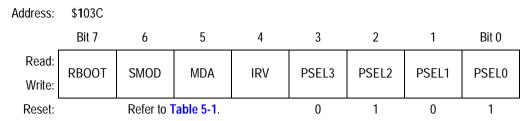

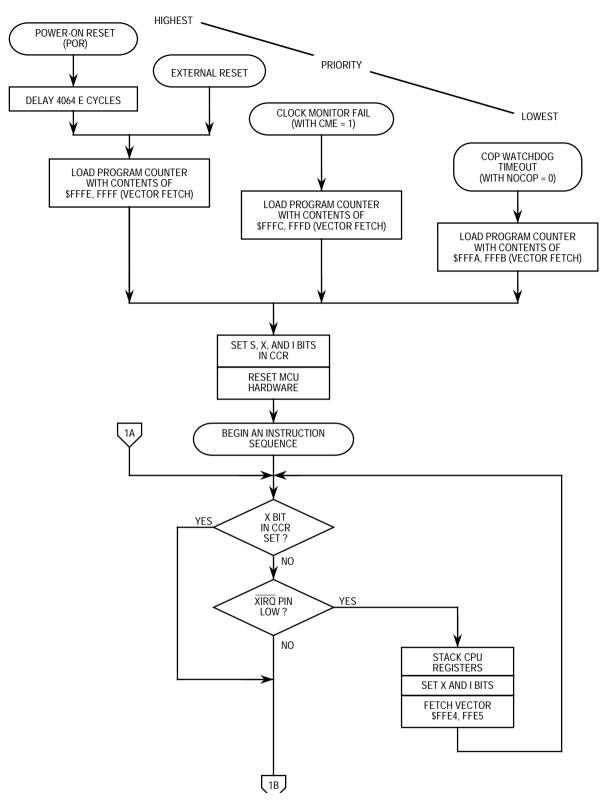

| 5-3   | Processing Flow Out of Resets                        | 182  |

| 5-4   | Interrupt Priority Resolution                        | 184  |

| 5-5   | Interrupt Source Resolution within SCI               | 186  |

| 6-1   | M68HC11 Programmer's Model                           | 199  |

| 7-1   | Parallel I/O Registers and Control Bits              | 234  |

| 7-2   | Pin Logic Registers and Control Bits                 |      |

|       |                                                      |      |

| Figur       | e Title                                          | Page |

|-------------|--------------------------------------------------|------|

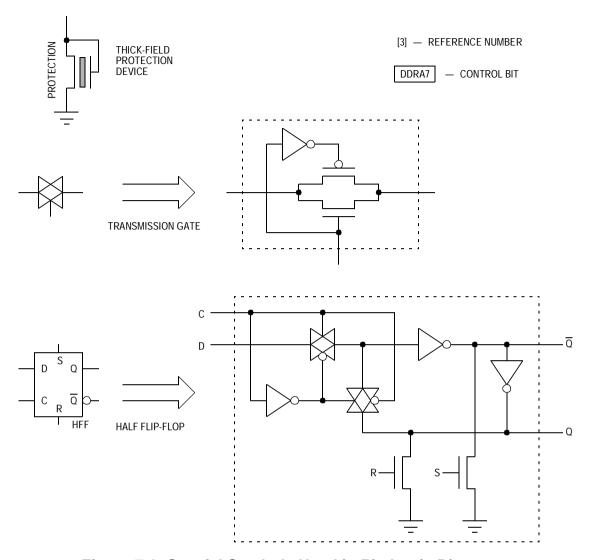

| 7-3         | Special Symbols Used in Pin Logic Diagrams       | 239  |

| 7-4         | PA2-PA0 (IC3-IC1) Pin Logic                      | 239  |

| 7-5         | PA6-PA3 (OC5-OC2) Pin Logic                      | 241  |

| 7-6         | PA7 (OC1 and PAI) Pin Logic                      | 243  |

| 7-7         | Idealized Port A Timing                          | 244  |

| 7-8         | Port B Pin Logic                                 | 246  |

| 7-9         | Idealized Port B Timing                          | 247  |

| 7-10        | $R/\overline{W}$ (STRB) Pin Logic                | 249  |

| 7-11        | Port C Expanded Mode Pin Logic                   | 252  |

| 7-12        | Summary of Idealized Port C Expanded Mode Timing | 254  |

| 7-13        | Port C Single-Chip Mode Pin Logic                | 255  |

| 7-14        | Idealized Port C Single-Chip Mode Timing         |      |

| 7-15        | AS (STRA) Pin Logic                              | 260  |

| 7-16        | PD0 (RxD) Pin Logic                              | 262  |

| 7-17        | PD1 (TxD) Pin Logic                              | 264  |

| 7-18        | PD2 (MISO) Pin Logic                             | 267  |

| 7-19        | PD3 (MOSI) Pin Logic                             |      |

| <b>7-20</b> | PD4 (SCK) Pin Logic                              |      |

| 7-21        | PD5 (SS) Pin Logic                               |      |

| 7-22        | Idealized Port D Timing                          | 277  |

| 7-23        | Port E Pin Logic                                 |      |

| 7-24        | Idealized Port E Timing                          |      |

| 7-25        | Idealized Timing for Simple Strobe Operations    |      |

| 7-26        | Idealized Timing for Full-Input Handshake        |      |

| 7-27        | Idealized Timing for Full-Output Handshake       |      |

| 7-28        | Parallel I/O Control Register (PIOC)             | 287  |

| 8-1         | CPHA Equals Zero SPI Transfer Format             | 294  |

| 8-2         | CPHA Equals One SPI Transfer Format              | 294  |

| 8-3         | SPI System Block Diagram                         | 296  |

| 8-4         | Port D Data Direction Register (DDRD)            | 299  |

| 8-5         | SPI Control Register (SPCR)                      | 300  |

| 8-6         | SPI Status Register (SPSR)                       | 302  |

| 8-7         | Delay from Write SPDR to Transfer Start (Master) | 307  |

| 8-8         | Transfer Ending for an SPI Master                | 308  |

| 8-9         | Transfer Ending for an SPI Slave                 | 308  |

|             |                                                  |      |

# List of Figures

| e Title                                       | Page                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Hardware Hookup for Examples 8-1 and 8-2      | 310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Register Definitions and RAM Variables        |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| for Examples 8-1 and 8-2                      | 310                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example 8-1 Software Listing)                 | 312                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Timing Analysis for Example 8-1               | 314                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Example 8-2 Software Listing                  | 315                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Timing Analysis for Example 8-2               | 316                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI Transmitter Block Diagram                 | 320                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI Receiver Block Diagram                    | 322                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

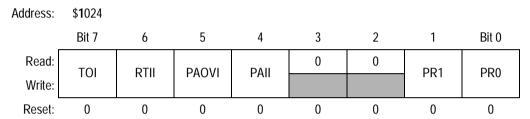

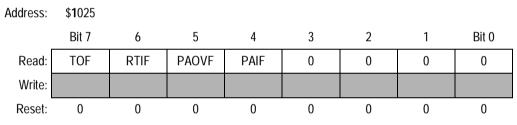

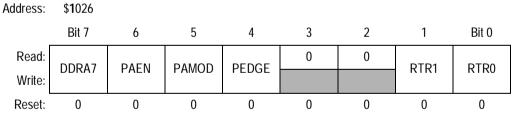

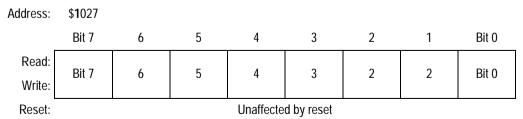

| Port D Related Registers                      | 325                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

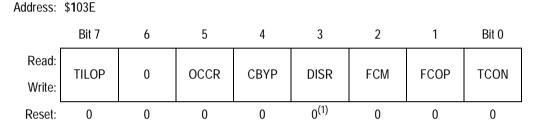

| Baud Rate Control Register (BAUD)             | 327                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI Control Register 1 (SCCR1)                | 329                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI Control Register 2 (SCCR2)                | 331                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI Status Register (SCSR)                    | 334                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| SCI Data Register (SCDR)                      | 337                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TxD Pin Logic Block Diagram                   | 345                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

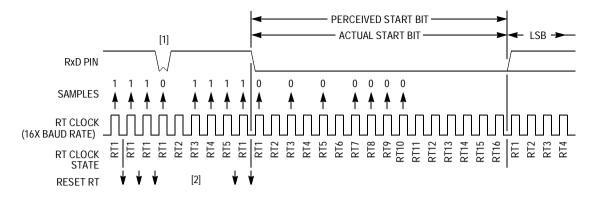

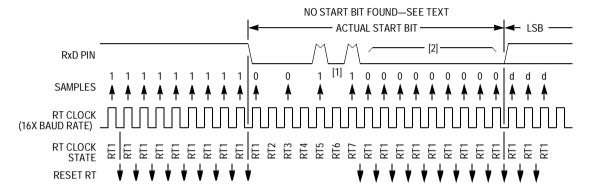

| Start Bit — Ideal Case                        | 348                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

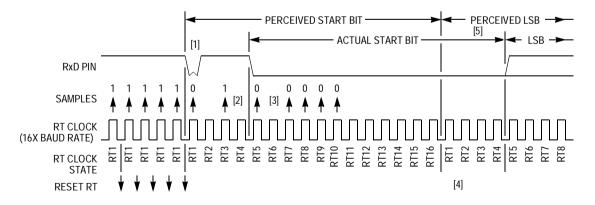

| Start Bit — Noise Case One                    | 349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

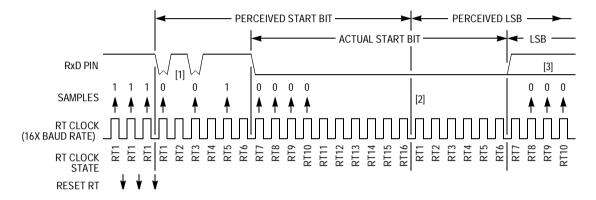

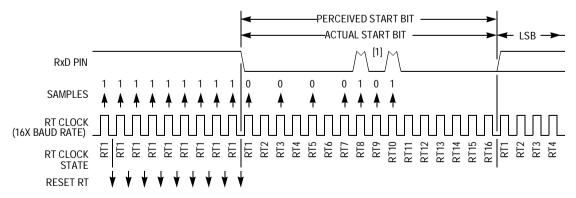

| Start Bit — Noise Case Two                    | 349                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

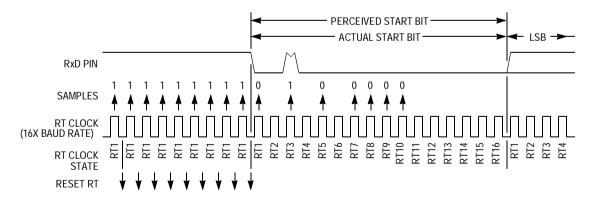

| Start Bit — Noise Case Three                  | 350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Start Bit — Noise Case Four                   | 350                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Start Bit — Noise Case Five                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |