# M68EVB912BC32/D1

October 1997

# M68EVB912BC32 EVALUATION BOARD USER'S MANUAL

Motorola reserves the right to make changes without further notice to any products herein to improve reliability, function or design. Motorola does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. Motorola products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Motorola product could create a situation where personal injury or death may occur. Should Buyer purchase or use Motorola products for any such unintended or unauthorized application, Buyer shall indemnify and hold Motorola and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Motorola was negligent regarding the design or manufacture of the part.

ii 68EVB912BC32UM

# TABLE OF CONTENTS

# CHAPTER 1 GENERAL INFORMATION

| 1.1 INTRODUCTION                        | 1-1        |

|-----------------------------------------|------------|

| 1.2 GENERAL DESCRIPTION AND FEATURES    | 1-1        |

| 1.3 FUNCTIONAL OVERVIEW                 | 1-4        |

| 1.4 EXTERNAL EQUPMENT REQUIREMENTS      | 1-6        |

| 1.5 EVB SPECIFICATIONS                  | 1-7        |

| 1.6 CUSTOMER SUPPORT                    | 1-8        |

| CHAPTER 2 CONFIGURATION AND SETU        | J <b>P</b> |

| 2.1 UNPACKING AND PREPARATION           | 2-1        |

| 2.2 EVB CONFIGURATION                   | 2-1        |

| 2.3 EVB TO POWER SUPPLY CONNECTION      | 2-2        |

| 2.4 EVB TO TERMINAL CONNECTION          | 2-2        |

| 2.5 TERMINAL COMMUNICATIONS SETUP       | 2-4        |

| 2.5.1 Communication Parameters          | 2-4        |

| 2.5.2 Dumb-Terminal Setup               | 2-4        |

| 2.5.3 Host-Computer Setup               | 2-4        |

| 2.5.4 Changing the Baud Rate            | 2-4        |

| CHAPTER 3 OPERATION                     |            |

| 3.1 OPERATING MODES                     | 3-1        |

| 3.1.1 EVB Mode                          | 3-1        |

| 3.1.2 JUMP-EEPROM Mode                  | 3-1        |

| 3.1.3 POD (Probe) Mode                  | 3-2        |

| 3.1.3.1 Target Types Supported          | 3-2        |

| 3.1.3.2 Target MCU Characteristics      | 3-2        |

| 3.1.3.3 Programming the Target's EEPROM | 3-3        |

| 3.1.3.4 Controlling Target Execution.   | 3-3        |

| 3.1.4 BOOTLOAD Mode                | 3-3  |

|------------------------------------|------|

| 3.2 STARTUP                        | 3-3  |

| 3.2.1 Startup Procedure            | 3-3  |

| 3.2.2 Operating Procedures         | 3-4  |

| 3.2.2.1 EVB Mode                   | 3-4  |

| 3.2.2.2 JUMP-EEPROM Mode           | 3-4  |

| 3.2.2.3 POD Mode                   | 3-5  |

| 3.2.2.4 BOOTLOAD Mode              | 3-6  |

| 3.3 RESET                          | 3-6  |

| 3.4 ABORTING A USER PROGRAM        | 3-6  |

| 3.5 USING D-BUG12 COMMANDS         | 3-7  |

| 3.5.1 Command-Line Prompt          | 3-7  |

| 3.5.2 Entering Commands            | 3-7  |

| 3.5.3 Command-Set Summary          | 3-8  |

| 3.6 D-BUG12 COMMAND SET            | 3-10 |

| Assembler/Disassembler             | 3-11 |

| Set Baud Rate                      | 3-14 |

| Block Fill                         | 3-15 |

| Breakpoint Set                     | 3-16 |

| Bulk Erase EEPROM                  | 3-18 |

| Call Subroutine                    | 3-19 |

| Specify Target MCU Device          | 3-20 |

| Specify Target EEPROM Base Address | 3-23 |

| Erase Target Flash EEPROM          | 3-25 |

| Program Target Flash EEPROM        | 3-27 |

| Go Execute a User Program          | 3-29 |

| Go Till                            | 3-30 |

| Onscreen Help Summary              | 3-31 |

| Load S-Record File                 | 3-33 |

| Memory Display                     | 3-34 |

| Memory Display, Word               | 3-35 |

| Memory Modify                      | 3-36 |

| Memory Modify, Word                | 3-38 |

| Move Memory Block                  | 3-40 |

| Remove Breakpoints                 | 3-41 |

| Register Display                                                                    | 3-42       |

|-------------------------------------------------------------------------------------|------------|

| Specify Target EEPROM Register Address                                              | 3-43       |

| Reset Target MCU                                                                    | 3-45       |

| Register Modify                                                                     | 3-46       |

| Stop Execution on Target MCU                                                        | 3-47       |

| Trace                                                                               | 3-48       |

| Display Memory in S-Record Format                                                   | 3-50       |

| Verify S-Record File against Memory                                                 | 3-51       |

| Modify Register Value                                                               | 3-52       |

| 3.7 OFF-BOARD CODE GENERATION                                                       | 3-54       |

| 3.8 MEMORY USAGE                                                                    | 3-54       |

| 3.8.1 Description                                                                   | 3-54       |

| 3.8.2 Memory Map                                                                    | 3-55       |

| 3.9 OPERATIONAL LIMITATIONS                                                         | 3-55       |

| 3.9.1 On-Chip RAM                                                                   | 3-56       |

| 3.9.2 On-Chip EEPROM                                                                | 3-56       |

| 3.9.3 SCI Port Usage                                                                | 3-56       |

| 3.9.4 Dedicated MCU Pins                                                            | 3-56       |

| 3.9.5 Terminal Communications                                                       | 3-57       |

| CHAPTER 4 HARDWARE REFERENCE                                                        |            |

| 4.1 PCB DESCRIPTION                                                                 | 4 1        |

| 4.1 PCB DESCRIPTION4.1 PCB DESCRIPTION4.2 CONFIGURATION HEADERS AND JUMPER SETTINGS |            |

| 4.3 POWER INPUT CIRCUITRY                                                           |            |

| 4.4 TERMINAL INTERFACE                                                              | 4-3<br>4-5 |

| 4.5 MICROCONTROLLER                                                                 |            |

| 4.6 CLOCK CIRCUITRY                                                                 |            |

| 4.7 RESET                                                                           |            |

| 4.8 LOW-VOLTAGE INHIBIT                                                             |            |

| 4.9 BACKGROUND DEBUG MODE (BDM) INTERFACE                                           |            |

| 4.10 PROTOTYPE AREA4.10                                                             |            |

| 4.10 PROTOT YPE AREA4.11 MCU CONNECTORS                                             |            |

|                                                                                     |            |

| 4.12 CAN PHYSICAL INTERFACE                                                         | 4-10       |

# APPENDIX A S-RECORD FORMAT

| DESCRIPTION                                       | A-1 |

|---------------------------------------------------|-----|

| S-RECORD CONTENT                                  | A-1 |

| S-RECORD TYPES                                    | A-2 |

| S-RECORD EXAMPLE                                  | A-3 |

|                                                   |     |

| APPENDIX B COMMUNICATIONS PROGRAM EXAMPLES        |     |

| INTRODUCTION                                      | B-1 |

| PROCOMM FOR DOS — IBM PC                          | B-1 |

| Setup                                             | B-1 |

| S-Record Transfers to EVB Memory                  | B-2 |

| KERMIT FOR DOS — IBM PC                           | B-3 |

| Setup                                             | B-3 |

| S-Record Transfers to EVB Memory                  | B-3 |

| KERMIT — SUN WORKSTATION                          | B-4 |

| Setup                                             | B-4 |

| S-Record Transfers to EVB Memory                  | B-4 |

| MACTERMINAL — APPLE MACINTOSH                     | B-5 |

| Setup                                             | B-5 |

| S-Record Transfers to EVB Memory                  | B-5 |

| RED RYDER — APPLE MACINTOSH                       | B-6 |

| Setup                                             | B-6 |

| S-Record Transfers to EVB Memory                  |     |

| ·                                                 |     |

| APPENDIX C D-BUG12 STARTUP CODE                   |     |

|                                                   |     |

| APPENDIX D D-BUG12 CUSTOMIZATION DATA             |     |

| INITIAL USER CPU REGISTER VALUES                  | D-2 |

| SysClk FIELD                                      | D-2 |

| IOBase FIELD                                      |     |

| SCIBaudRegVal FIELD                               |     |

| EEBase AND EESize FIELDS                          |     |

| EEPROM ERASE/PROGRAM DELAY FUNCTION POINTER FIELD | D-4 |

| AUXILIARY COMMAND TABLE ENTRIES                   | D-4 |

| APPENDIX E | EEPROM BOOTLOADER |

|------------|-------------------|

|            |                   |

| SERIAL S-RECORD BOOTLOADER                          | E-1  |

|-----------------------------------------------------|------|

| (E)rase                                             |      |

| (P)rogram                                           |      |

| (L)oadEE                                            |      |

| VECTOR JUMP TABLE: INTERRUPT AND RESET ADDRESSES    |      |

| RELOADING AND CUSTOMIZING D-BUG12                   |      |

| Obtaining D-Bug12 Upgrades                          |      |

| Reloading D-Bug12  Customizing D-Bug12              |      |

| Customizing D-Bug12                                 | E-3  |

| INDEX                                               |      |

|                                                     |      |

| LIST OF ILLUSTRATIONS                               |      |

| Figure 1-1. EVB Layout and Component Placement      | 1-3  |

| Figure 1-2. EVB Solder Side View                    | 1-4  |

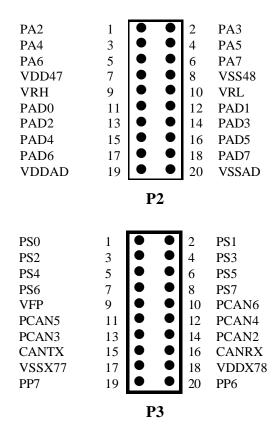

| Figure 4-2. MCU I/O Headers P2, P3                  | 4-9  |

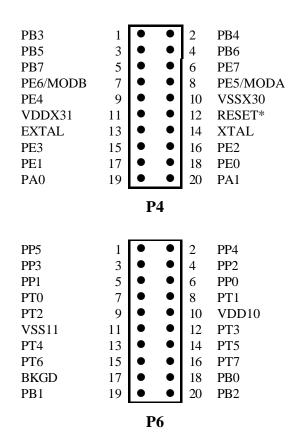

| Figure 4-3. MCU I/O Headers P4, P6                  | 4-10 |

| LIST OF TABLES                                      |      |

| Table 1-1. EVB Specifications                       | 17   |

| Table 2-1. EVB Startup Mode Jumpers                 |      |

|                                                     |      |

| Table 2-2. RS-232C Interface Cabling                |      |

| Table 2-3. Communication Parameters                 |      |

| Table 3-1. D-Bug12 Command-Set Summary              |      |

| Table 3-2. M68HC11 to CPU12 Instruction Translation | 3-12 |

| Table 3-3. CPU12 Registers                          | 3-52 |

| Table 3-4. Condition Code Register Bits             | 3-52 |

| Table 3-5. Factory-Configuration Memory Map         | 3-55 |

# **CONTENTS**

| Table 4-1. | Jumper and Header Functions4  | 3    |

|------------|-------------------------------|------|

| Table 4-2. | CPU Mode Selection            | .4-6 |

| Table 4-3. | BDM Connector Pin Assignments | .4-8 |

viii 68EVB912BC32UM/D

68EVB912BC32UM/D ix

# CHAPTER 1 GENERAL INFORMATION

#### 1.1 INTRODUCTION

This manual provides the necessary information for using the M68EVB912BC32 Evaluation Board (the EVB), an evaluation, debugging, and code-generation tool for the MC68HC912BC32 Microcontroller Unit (MCU) devices. The manual includes:

- A general description of the EVB

- Configuration and setup instructions

- Startup and operating instructions

- Detailed descriptions of the operating firmware's command set

- A detailed hardware-reference section

- Appendices containing reference data

Additional reference items, such as schematic diagrams and parts lists, are shipped as part of the EVB package.

#### 1.2 GENERAL DESCRIPTION AND FEATURES

The EVB is an economical tool for designing and debugging code for, and evaluating the operation of, the MC68HC912BC32 MCU. By providing the essential MCU timing and I/O circuitry, the EVB simplifies user evaluation of prototype hardware and software.

The board consists of a 5.15 by 3.4 inch (13.1 by 8.64 cm) four layer printed circuit board (PCB) that provides the platform for interface and power connections to the MC68HC912BC32 MCU chip.

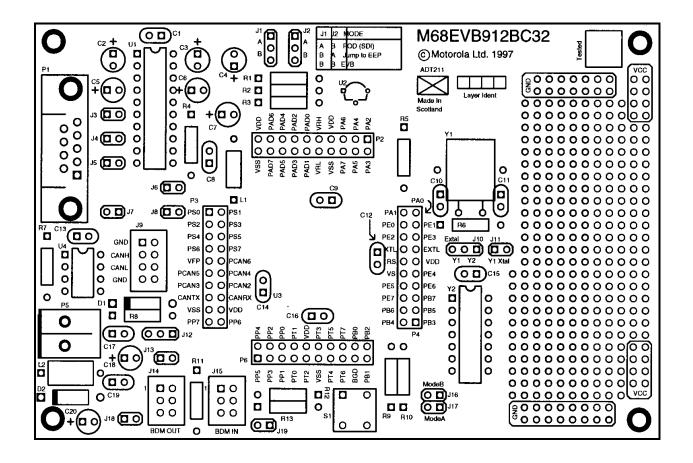

Figure 1-1 shows the EVB's layout and locations of the major components, as viewed from the component side of the board.

#### **Hardware features** of the low-cost EVB include:

- Four layer PCB

- Single-supply +5 Vdc power input (P5)

- RS-232C interface

- BDM IN and BDM OUT connectors for remote debugging of a user's target system

68EVB912BC32UM/D 1-1

- Header footprints for access to all MCU pins

- 16-MHz oscillator module for 8-MHz bus operation

- Headers for jumper selection of and connection to hardware options:<sup>(1)</sup>

- RS-232 isolation (J6, J8)

- EVB mode selection (J1, J2)

- MCU mode selection (J16, J17)

- Vpp/Vdd selection (J12)

- Vpp input (J13)

- BDM IN (J15)

- BDM OUT Vdd/reset disconnects (J18, J19)

- BDM OUT (J14)

- Low-Voltage Inhibit (LVI)

- EXTAL source control and access (J10)

- Can Physical Interface (J9)

- Four 2x20 header connectors for access to the MCU's I/O lines (P2, P3, P4, and P6)

- Prototype expansion area for customized interfacing with the MCU

- Low-profile reset push-button switch (S1)

- Low-voltage inhibit protection (U2)

- CAN Physical Interface (U4)

#### **Firmware features** include:

- The D-Bug12 monitor/debugger program, resident in on-chip Flash EEPROM

- Full support for either dumb-terminal or host-computer terminal interface

- Single-line assembler/disassembler

- File-transfer capability from a host computer to RAM or EEPROM, allowing off-board code generation

- Ability to program EEPROM on either the host EVB or a compatible target system

1-2 68EVB912BC32UM/D

<sup>(1)</sup> For full details of the jumper settings, refer to **Table 4-1**.

Figure 1-1. EVB Layout and Component Placement

68EVB912BC32UM/D 1-3

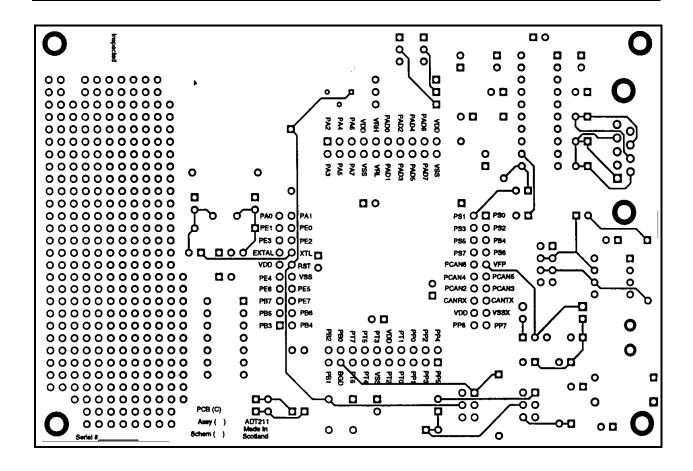

Figure 1-2. EVB Solder Side View

#### 1.3 FUNCTIONAL OVERVIEW

The EVB is factory-configured to execute DBug12, the Flash EEPROM-resident monitor program, without further configuration by the user. It is ready for use with an RS-232C terminal for writing and debugging user code. Follow the setup instructions in Chapter 2 to prepare for operation.

The EVB can also be jumper-configured to:

- run a program directly out of EEPROM

- control a remote "pod" MCU via the Background Debug Mode interface

- reprogram EEPROM on either the host EVB or the "pod"

For the correct jumper settings, refer to 4.2 Configuration Headers and Jumper Settings.

1-4 68EVB912BC32UM/D

#### **NOTES**

The D-Bug12 operating instructions in this manual presume the factory-default memory configuration. Other configurations require different operating-software arrangements.

EEPROM resides in two areas of memory (refer to Table 3-5), which are referred to in this manual as "byte-erasable EEPROM" and "Flash EEPROM." This distinction is necessary because of the different ways in which they may be programmed and used.

D-Bug12 uses the MCU's Serial Communications Interface (SCI) for communications with the user terminal. For information on the port and its connector, refer to **2.4 EVB to Terminal Connection** and **4.4 Terminal Interface**.

If the MCU's single-wire Background Debug Mode (BDM) interface serves as the user interface, the SCI port becomes available for user applications. This mode requires either:

- another M68EVB912BC32 (or other suitable HC12 EVB) and a host computer

- a background debug development tool, such as Motorola's Serial Debug Interface (SDI)

For more information, refer to the *Motorola Serial Debug Interface User's Manual*.

Two methods may be used to generate EVB user code:

- 1. For small programs or subroutines, D·Bug12's single-line assembler/disassembler may be used to place object code directly into the EVB's RAM or EEPROM.

- 2. For larger programs, P&E Microcomputer Systems' IASM12 may be used on a host computer to generate S-Record object files, which can then be loaded into the EVB's memory using D-Bug12's LOAD command.

The EVB features a prototype area, which allows custom interfacing with the MCU's I/O and bus lines. These connections are broken out via headers P2, P3, P4, and P6, which are immediately adjacent to the MCU on the board. Wire-wrap pins may be placed in these headers to connect to the prototyping area, as shown in Figure 1-1.

An on-board push-button switch, S1, provides for resetting the EVB hardware and restarting D-Bug12.

The EVB can begin operation in any of four jumper-selectable (J1, J2) modes at reset:

- 1. In **EVB mode**, program execution begins in one of two ways:

- a. If D-Bug12 is resident in Flash EEPROM (i.e., if Mode 4 below has *not* been performed), D-Bug12 immediately issues its command prompt on the terminal display and waits for a user entry.

- b. If D-Bug12 has been replaced in Flash EEPROM with user code (i.e., Mode 4 below *has* been performed), execution begins with the user program.

68EVB912BC32UM/D 1-5

- 2. In **JUMP-EE mode**, execution begins directly at location \$0D00 with the user code in byte-erasable EEPROM.

- 3. In **POD mode**, the board makes use of the BDM OUT header (J14) and uses the D-Bug12 commands to non-intrusively interrogate an external target MCU. Special prompts are displayed to let the user know if this mode is selected. If no external MCU is detected, the software informs the user.

- The target's EEPROM may be programmed while the host M68EVB912BC32 board is in EVB mode, using the D-Bug12 commands BULK, LOAD, FBULK and FLOAD.

- 4. In **BOOTLOAD mode**, the host EVB's byte-erasable or Flash EEPROM may be reprogrammed with user code. This mode may also be used to reload or customize D-Bug12.

D-Bug12 allows programming of the MC68HC912BC32's on-chip EEPROM through commands that directly alter memory. For details of all D-Bug12 commands, refer to **3.6 D-Bug12 Command Set**.

When operating in EVB mode, the MCU must manage the EVB hardware and execute DBug12 *in addition* to serving as the user-application processor, there are a few restrictions on its use. For more information, refer to **3.9 Operational Limitations**.

# 1.4 EXTERNAL EQUPMENT REQUIREMENTS

In addition to the EVB, the following user-supplied external equipment is required:

- Power supply see Table 1-1 for voltage and current requirements.

- User terminal options:

- RS-232C dumb terminal allows single-line on-board code assembly and disassembly.

- Host computer with RS-232C serial port allows off-board code assembly that can be loaded into the EVB's memory. Requires a user-supplied communications program capable of emulating a dumb terminal. Examples of acceptable communications programs are given in Appendix B ¾ Communications Program Examples.

- Host computer using the MCU's BDM interface frees the target MCU's SCI port for user applications. This requires another M68EVB912BC32 for use as the target or a background debug development tool, such as the Motorola Serial Debug Interface (SDI).

- Power-supply and terminal interconnection cables as required

For full details of equipment setup, cabling, and special requirements, refer to Chapter 2.

1-6 68EVB912BC32UM/D

# 1.5 EVB SPECIFICATIONS

Table 1-1 lists the EVB specifications.

**Table 1-1. EVB Specifications**

| Characteristic                               | Specifications                                                                                |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------|--|

| MCU                                          | MC68HC912BC32                                                                                 |  |

| MCU I/O ports                                | HCMOS compatible                                                                              |  |

| Background Debug Mode interface (IN and OUT) | two 2x3 headers                                                                               |  |

| Communications port                          | RS-232C DCE port                                                                              |  |

| Power requirements,<br>16 MHz clock source   | +2.7 Vdc to +5.0 Vdc @ 100 mA (max.) For low-voltage operation, refer to section 4.8.         |  |

| Prototype area: Area Holes                   | approx. 1.5 x 3 in. (3.8 x 7.6 cm)<br>approx. 11 wide x 28 high, on 0.1 in. (2.54 mm) centers |  |

| Board dimensions                             | 5.15 x 3.4 in. (13.1 x 8.64 cm)                                                               |  |

68EVB912BC32UM/D 1-7

#### 1.6 CUSTOMER SUPPORT

AUSTRALIA, **JAPAN** Melbourne – (61-3)887-0711 Fukuoka – 81-92-725-7583 Sydney -(61-2)906-3855Gotanda – 81-3-5487-8311 BRAZIL Nagoya - 81-52-232-3500 Osaka - 81-6-305-1802 Sao Paulo – 55(11)815-4200 Sendai - 81-22-268-4333 CANADA B.C., Vancouver – (604)606-8502 Takamatsu – 81-878-37-9972 ONTARIO, Toronto – (416)497-8181 Tokyo - 81-3-3440-3311 ONTARIO, Ottawa – (613)226-3491 **KOREA** QUEBEC, Montreal – (514)333-3300 Pusan – 82(51)4635-035 **CHINA** Seoul - 82(2)554-5118Beijing – 86-10-6843722 MALAYSIA **FINLAND** Penang -60(4)374514Helsinki – 358-9-6824-400 **MEXICO FRANCE** Mexico City -52(5)282-0230Guadalajara – 52(36)21-8977 Paris – 33134 635900 PUERTO RICO **GERMANY** Langenhagen/Hannover – 49(511)786880 San Juan - (809)282-2300 Munich – 49 89 92103-0 SINGAPORE - (65)4818188 Nuremberg – 49 911 96-3190 SPAIN Sindelfingen – 49 7031 79 710 Madrid - 34(1)457-8204Wiesbaden – 49 611 973050 **SWEDEN** HONG KONG Solna – 46(8)734-8800 Kwai Fong – 852-6106888 **SWITZERLAND** Tai Po – 852-6668333 Geneva - 41(22)799 11 11 Zurich - 41(1)730-4074 INDIA Bangalore – (91-80)5598615 **TAIWAN** Taipei – 886(2)717-7089 **ISRAEL THAILAND** Herzlia – 972-9-590222 **ITALY** Bangkok - 66(2)254-4910 Milan - 39(2)82201**UNITED KINGDOM** Aylesbury – 44 1 (296)395252 **UNITED STATES** Phoenix, AZ – 1-800-441-2447

For a list of the Motorola sales offices and distributors: http://www.mcu.mot.sps.com

1-8 68EVB912BC32UM/D

# CHAPTER 2 CONFIGURATION AND SETUP

# 2.1 UNPACKING AND PREPARATION

Verify that the following items are present in the EVB package:

- The M68EVB912BC32 board assembly

- Background Debug Mode(BDM) interface cable, 6-pin to 6-pin

- EVB schematic diagram and parts list

Save all packing materials for storing and shipping the EVB.

Remove the EVB from its anti-static container.

# 2.2 EVB CONFIGURATION

Because the EVB has been factory-configured to operate with D-Bug12, it is not necessary to change any of the jumper settings to begin operating immediately.

As shown in Table 2-1, only two jumpers (J1 and J2) should be changed during the course of factory-default EVB operation with D-Bug12.

68EVB912BC32UM/D 2-1

**Table 2-1. EVB Startup Mode Jumpers**

|    | nper<br>tions | Startup Mode                                                                                                                                    |  |

|----|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--|

| J1 | J2            |                                                                                                                                                 |  |

| В  | В             | EVB execution mode (default). D-Bug12 is executed from Flash EEPROM upon reset. The D-Bug12 prompt appears immediately on the terminal display. |  |

| В  | А             | JUMP-EEPROM mode. User code is executed from byte-erasable EEPROM upon reset. For more information, refer to <b>3.1 Operating Modes</b> .       |  |

| Α  | В             | Remote Debugging through BDM OUT header (J14)                                                                                                   |  |

| А  | Α             | BOOTLOAD mode                                                                                                                                   |  |

Other jumper settings affect the hardware setup and/or MCU operational modes. For an overview of all jumper-selectable functions, refer to **1.2 General Description and Features**. For details of the settings, see Table 4-1.

#### 2.3 EVB TO POWER SUPPLY CONNECTION

The EVB requires a user-provided external power supply. See Table 1-1 for the voltage and current specifications. For full details of the EVB's power-input circuitry, refer to **4.3 Power Input Circuitry**.

A power supply with current-limiting capability is desirable. If this feature is available on the power supply, set it at 200 mA.

Connect the external power supply to connector P5 on the EVB, using 20 AWG or smaller insulated wire. Strip each wire's insulation 1/4 in. from the end, lift the P5 contact lever to release tension on the contact, insert the bare end of the wire into P5, and close the lever to secure the wire. Observe the polarity carefully.

#### **CAUTION**

Do not use wire larger than 20 AWG in connector P5. Larger wire could damage the connector.

#### 2.4 EVB TO TERMINAL CONNECTION

For factory-default operation, connect the terminal to P1 on the EVB, as shown in Table 2-2. This setup uses the MCU's SCI port and its associated RS-232C interface for communications with the terminal device.

2-2 68EVB912BC32UM/D

Standard, commercially available cables may be used in most cases. Note that the EVB requires only three of the RS-232C signals. Table 2-2 lists these signals and their pin assignments. Other signals have been routed through the RS-232C interface chip for proper levels. Some terminal interface programs require proper levels on all pins to function correctly.

The EVB's RS-232C connector, P1, is wired as Data Circuit-terminating Equipment (DCE) and employs a 9-pin subminiature D (DB-9) receptacle.

Most terminal devices — whether dumb terminals or the serial ports on host computers — are wired as Data Terminal Equipment (DTE) and employ 9- or 25-pin subminiature D (DB-9 or DB-25) plugs. In these cases, normal straight-through cabling is used between the EVB and the terminal. Adapters are readily available for connecting 9-pin cables to 25-pin terminal connectors.

If the terminal device is wired as DCE, the RXD and TXD lines must be cross-connected, as shown in Table 2-2. Commercial "null modem" adapter cables are available for this purpose.

| EVB P1            | DTE Signal          | Terminal                   |       |                                  |       |

|-------------------|---------------------|----------------------------|-------|----------------------------------|-------|

| DCE<br>Receptacle |                     | DTE <sup>(1)</sup><br>Plug |       | DCE <sup>(2)</sup><br>Receptacle |       |

|                   |                     | DB-9                       | DB-25 | DB-9                             | DB-25 |

| 2                 | Receive Data (RXD)  | 2                          | 2     | 3                                | 3     |

| 3                 | Transmit Data (TXD) | 3                          | 3     | 2                                | 2     |

| 5                 | Ground (GND)        | 5                          | 7     | 5                                | 7     |

Table 2-2. RS-232C Interface Cabling

Optionally, the MCU's Background Debug Mode (BDM IN — J15) interface can serve as the user interface. This setup makes the SCI port available for user applications. Additional hardware and software are required. For more information, refer to the documentation for the background debug development tool being used. This can be another M68EVB912BC32 or a tool such as Motorola's Serial Debug Interface (SDI).

68EVB912BC32UM/D 2-3

<sup>(1)</sup> Normal (DCE-to-DTE) cable connections

<sup>(2)</sup> Null modem (DCE-to-DCE) cable connections

# 2.5 TERMINAL COMMUNICATIONS SETUP

#### 2.5.1 Communication Parameters

The EVB's serial communications port uses the communication parameters listed in Table 2-3. Of these, only the baud rate can be changed. For instructions on changing it, refer to **2.5.4 Changing the Baud Rate**.

**Table 2-3. Communication Parameters**

| Baud Rate | 9600 |

|-----------|------|

| Data Bits | 8    |

| Stop Bits | 1    |

| Parity    | none |

#### 2.5.2 Dumb-Terminal Setup

Configuring a dumb terminal for use with the EVB consists of setting its parameters as shown in Table 2-3. Many terminals are configurable with externally accessible switches, but the procedure differs between brands and models. Consult the manufacturer's instructions for the terminal being used.

# 2.5.3 Host-Computer Setup

One advantage of using a host computer as the EVB's terminal is the ability to generate code off-board, for subsequent loading into the EVB's memory. It is thus desirable for the host to be capable of running programs such as P&E Microcomputer Systems' IASM12. For more information, refer to **3.7 Off-Board Code Generation**.

To serve as the EVB's terminal, the host computer must have an RS-232C serial port and an installed communications program capable of operating with the parameters listed in Table 2-3.

Setting up the parameters is normally done within the communications program, after it has been started on the host. Usually, the setup can be saved in a configuration file so that it does not have to be repeated. Procedures vary between programs; consult the user's guide for the specific program.

**Appendix B ¾ Communications Program Examples** provides examples of using some of the commonly available communications programs.

# 2.5.4 Changing the Baud Rate

The EVB's default baud rate for the RS-232C port is 9600. This can be changed in two ways:

2-4 68EVB912BC32UM/D

- For temporary changes, use the D-Bug12 BAUD command. This change remains in effect only until the next reset or power-up, at which time the baud rate returns to 9600.

- For permanent changes, the D-Bug12 baud-rate initialization value stored in Flash EEPROM must be modified. For instructions, refer to **Appendix D ¾ D-Bug12 Customization Data** and **Appendix E ¾ EEPROM Bootloader**.

68EVB912BC32UM/D 2-5

2-6 68EVB912BC32UM/D

# CHAPTER 3 OPERATION

#### 3.1 OPERATING MODES

The EVB can operate in one of four jumper-selectable modes:

**EVB mode** — either D-Bug12 or the user code in Flash EEPROM executes.

**JUMP-EEPROM mode** — user code in byte-erasable EEPROM executes.

**POD mode** — D-Bug12 executes. EVB serves as the BDM probe for a target system.

**BOOTLOAD mode** — the host EVB's EEPROM may be reprogrammed.

The operating mode is determined by jumper headers J1 and J2, as shown in **Table 4-1**. The modes are described in the following three sections.

#### **NOTE**

When operating in EVB mode, the M68EVB912BC32 cannot fully emulate a target system. The limitations are described in **3.9 Operational Limitations**.

Target system emulation may, however, be performed by using the EVB with D-Bug12 as an intelligent, non-intrusive BDM interface. This operation is described in **3.1.3 POD** (**Probe**) **Mode**.

#### **3.1.1 EVB Mode**

In the default EVB mode (J1: pos. B and J2: pos. B), D-Bug12 begins execution immediately. The D-Bug12 prompt appears on the terminal and commands may be entered as described in **3.5 Using D-Bug12 Commands**.

If D-Bug12 has been replaced with user code in Flash EEPROM, execution begins with the user's program.

#### 3.1.2 JUMP-EEPROM Mode

In this mode (J1: pos. B and J2: pos. A), the EVB begins operation out of reset by executing the user program in byte-erasable EEPROM starting at address \$0D00, as shown in Table 3-5.

68EVB912BC32UM/D 3-1

This mode is effected using the MCU's PAD0 line. User code may be programmed into byte-erasable EEPROM using the D-Bug12 commands listed in **3.5.3 Command-Set Summary**.

Control can be returned to D-Bug12 in the following ways:

- 1. Move the jumpers on headers J1 and J2 to position B and reset the EVB.

- 2. Terminate the user program with code that returns to D-Bug12 after execution has finished.

To return to D-Bug12 automatically after a user program has finished, include the following lines as the last instructions to be executed in the program:

```

STACKTOP: equ $0c00 ; stack at top of on-chip RAM AltResetVect: equ $F7FE;

lds #STACKTOP

jmp [AltResetVect, PCR] ; jump to start of D-Bug12

```

#### 3.1.3 POD (Probe) Mode

In this mode (J1: pos. A and J2: pos. B), the EVB and D-Bug12 serve as a POD ("probe") interface between a target system and the user. Communications between the EVB and the target are by means of the Background Debug Mode (BDM) interface, using the EVB header J14 (BDM OUT).

This arrangement allows the target system to perform true emulation of an application, as the BDM interface is non-intrusive upon the target's foreground operation. The target's on-chip resources are all available for the application. The target may be a second M68EVB912BC32 board or any other M68HC12 system. D-Bug12 commands are entered as usual on the user terminal, which is served by the POD EVB.

#### 3.1.3.1 Target Types Supported

All members of the M68HC12 family may be used in the target system.

#### 3.1.3.2 Target MCU Characteristics

The following DBug12 commands must be used to inform DBug12 of the target MCU's essential operating characteristics in order to allow transparent modification of the target's EEPROM. For details, refer to the command descriptions in **3.6 D-Bug12 Command Set**.

```

DEVICE — specifies the target's microprocessor type

EEBASE — specifies the base address of the target's Flash EEPROM

REGBASE — specifies the base address of the target MCU's I/O registers

```

3-2 68EVB912BC32UM/D

# 3.1.3.3 Programming the Target's EEPROM

The target MCU's on-chip byte-erasable or Flash EEPROM may be programmed from user-assembled S-Records on the host (terminal) computer by using the D-Bug12 commands BULK, LOAD, FBULK, and FLOAD. For details, refer to **3.6 D-Bug12 Command Set**.

#### 3.1.3.4 Controlling Target Execution

All D-Bug12 commands that control the execution of user code may also be used in both EVB mode and POD mode. Two additional commands are available in POD mode:

- RESET resets the target MCU and places it in active background mode

- STOP halts program execution on the target

For details, refer to the command descriptions in 3.6 D-Bug12 Command Set.

#### 3.1.4 BOOTLOAD Mode

In this mode (J1: pos. A and J2: pos. A), a user program may be loaded into the host EVB's byte-erasable or Flash EEPROM. D-Bug12 may be replaced as the startup "boot" program. This mode may also be used to reload or customize D-Bug12. The procedures are described in **Appendix E ¾ EEPROM Bootloader**.

#### 3.2 STARTUP

#### **3.2.1 Startup Procedure**

The following startup procedure includes a checklist of configuration and setup items. To begin operating the M68EVB912BC32, follow these steps::

- 1. Configure the EVB if required section 2.2.

- 2. Determine whether execution should begin in EVB mode (page 3-1), JUMP-EEPROM mode (page 3-1), POD mode (page 3-2), or BOOTLOAD mode (page 3-3). Set the jumpers on headers J1 and J2 accordingly sections 2.2 and 3.1.

- 3. Connect the EVB to the external power supply section 2.3.

- 4. Connect the EVB to the terminal section 2.4.

- 5. Configure the terminal communications interface section 2.5.

68EVB912BC32UM/D 3-3

- 6. Apply power to the EVB and to the terminal. If the terminal is a host computer,

- a. Verify that it has booted correctly.

- b. Start the communications program for terminal emulation section 2.5.3 and **Appendix B 3/4 Communications Program Examples**.

- 7. Reset the EVB by pressing and releasing the on-board reset switch (S1).

# 3.2.2 Operating Procedures

After starting the EVB in accordance with section 3.2.1, follow the operating procedure for the EVB mode that was selected: EVB mode, JUMP-EEPROM mode, POD mode, or BOOTLOAD mode. These procedures are described in the following sections.

#### **3.2.2.1** EVB Mode

In EVB mode, the MC68HC912BC32 begins executing code at the address contained in the alternate reset vector at \$F7FE (for information on the alternate reset and interrupt vector table, see **Vector Jump Table: Interrupt and Reset Addresses** on page E-3). The code pointed to by the alternate reset vector may either be D-Bug12 (factory default) or a user's program that has replaced D-Bug12 in Flash EEPROM.

**D-Bug12** — upon reset, the D-Bug12 sign-on banner and prompt should appear on the terminal's display as follows:

```

D-Bug12 v 2.0.0

Copyright 1996 - 1997 Motorola Semiconductor

For Commands type "Help" >

```

If the prompt does not appear, check all connections and verify that startup steps 1 through 7 in section 3.2.1 have been performed correctly.

When the prompt appears, D-Bug12 is ready to accept commands from the terminal as described in section 3.5.

User boot program — upon reset, the user program executes immediately. D-Bug12 commands are not available. Terminal communications take place either via the SCI under control of the user program or via the BDM interface and a serial debug interface tool such as Motorola's SDI.

#### 3.2.2.2 JUMP-EEPROM Mode

In JUMP-EEPROM mode, the user code in byte-erasable EEPROM starting at address \$0D00 is executed immediately. Terminal communications are controlled by the user code via the SCI or by an appropriate serial debug tool via the BDM interface. For more information, refer to **3.1.2 JUMP-**

3-4 68EVB912BC32UM/D

**EEPROM Mode**. Control can be returned to the DBug12 terminal prompt by doing one of the following:

- 1. terminating the user code with appropriate instructions see section 3.1.2

- 2. pressing the reset button (S1)

#### 3.2.2.3 POD Mode

In POD mode, the host EVB serves as a non-intrusive controller for the target system via the BDM interface. The host EVB begins executing code at the address contained in the alternate reset vector at \$F7FE (for information on the alternate reset and interrupt vector table, see **Vector Jump Table: Interrupt and Reset Addresses** on page E-3). The code pointed to by the alternate reset vector may either be D-Bug12 (factory default) or a user's program that has replaced D-Bug12 in Flash EEPROM.

**D-Bug12** — upon power-up or reset, D-Bug12 attempts to establish communications with a target system connected to BDM OUT (J14). Communications are first attempted without resetting the target system. If communications cannot be established, the following message is displayed:

```

Can't Communicate With The Target Processor To reset target, hit any key...

```

Pressing any key on the terminal's keyboard causes D-Bug12 to assert the target's reset pin for approximately 2 mS and try again to establish communications. If communications fail, the above error message is redisplayed. Once communications have been established with the target system, the D-Bug12 sign-on banner and prompt should appear on the terminal's display as follows:

```

D-Bug12 v 2.0.0

Copyright 1996 - 1997 Motorola Semiconductor

For Commands type "Help"

S>

```

If communications cannot be established with the target system after repeated attempts, check for the following possible problems:

- The host EVB's BDM OUT (J14) must be properly connected to the target system's BDM connector. If the target system is another EVB, make sure that the host EVB's BDM OUT is connected to target EVB's BDM IN (J15 for M68EVB912BC32).

- If the target system is not another EVB, verify that its BDM connector is wired to the proper MCU signals on each pin.

- If the target MCU does not have any firmware to execute, it could "run away," possibly executing a STOP opcode and preventing BDM communications with the host EVB.

Thus, it is *strongly* recommended that, if the target system does not have firmware to execute at reset, the target MCU be initially configured to begin operation in Special Single Chip mode. Resetting the target MCU in Special Single Chip mode places it in active

68EVB912BC32UM/D 3-5

background mode. See the target MCU's technical summary for details on setting the MCU operating mode.

Special D-Bug12 command-line prompts indicate the status of the target system:

S> target is in active background mode

R> target is running a user program

In addition to the normal D-Bug12 commands that control execution of user code, the RESET and STOP commands are available in POD mode. These commands are described in **3.6 D-Bug12 Command Set**.

D-Bug12 must be informed of the target MCU's basic operating parameters. Refer to section 3.1.3 for more information about setting up and using POD mode.

**User boot program** — upon reset, the user program executes immediately. D-Bug12 commands are not available. Communications with the user terminal and with the target system are controlled by the user program.

#### 3.2.2.4 BOOTLOAD Mode

In BOOTLOAD mode, a user program may be loaded into the host EVB's byte-erasable or Flash EEPROM. If the user code replaces DBug12 in Flash EEPROM, it serves as the "boot" program when the EVB is restarted in EVB or POD mode. This procedure is described in **Appendix E ¾ EEPROM Bootloader**.

#### 3.3 RESET

EVB operation can be restarted at any time by activating the hardware reset function. Do this in one of two ways:

- 1. Press and release the on-board reset switch, S1 (always applicable).

- 2. Activate the external reset input if one has been provided for operation below 3.0 Vdc.

Note that the EVB's reset circuitry is associated with the low-voltage protection. For more information, refer to **4.7 Reset** and **4.8 Low-Voltage Inhibit**.

# 3.4 ABORTING A USER PROGRAM

When operating in EVB mode, the only way to recover from an erroneous or runaway user program is to press the reset switch (S1). If this becomes necessary, the jumpers on headers J1 and J2 should be set to execute D-Bug12 at reset instead of the flawed user program.

3-6 68EVB912BC32UM/D

When operating in POD mode, the D-Bug12 RESET or STOP command can be used to regain control of the target system.

#### 3.5 USING D-BUG12 COMMANDS

D-Bug12, the EVB's firmware-resident monitor program, provides a self-contained operating environment that allows writing, evaluation, and debugging of user programs.

# 3.5.1 Command-Line Prompt

D-Bug12 displays one of three command-line prompts, depending upon its operating mode and/or the state of the target system. When D-Bug12 is operating in the EVB mode, it displays the single character ">" at the beginning of a line when it is waiting for the user to enter a command. When a command is issued that causes user code to run, D-Bug12 places the terminal cursor on a blank line, where it remains until control returns to D-Bug12.

When operating in the POD mode, D-Bug12 displays one of two prompts, depending upon the state of the attached target system. When the target system is in active background mode (not running a user program), the two-character prompt "S>" is displayed, indicating that the target is stopped and not running a user program. When the target system is running a user program, the two-character prompt "R>" is displayed, indicating that the target is running a user program.

Because the M68HC12 Background Debug Mode interface allows the reading and writing of target system memory even when the target is running a user's program, the probe microcontroller is always available for the entry of commands. D-Bug12 commands that examine or modify target system memory may be issued when either the "S>" or "R>" prompt is displayed.

#### 3.5.2 Entering Commands

Commands are typed on the terminal's DBug12 prompt line and executed when the carriage-return (ENTER) key is pressed. DBug12 then displays either the appropriate response to the command or an error indication.

The D-Bug12 command-line prompt is the greater-than sign (>). Type the command and any other required or optional fields immediately after the prompt, as follows:

#### command-line syntax:

```

<command> [<parameter>] ...[<parameter>]<ENTER>

```

#### where:

68EVB912BC32UM/D 3-7

<ENTER>

is the terminal keyboard's carriage-return or enter key.

#### **NOTES**

1. The command-line syntax is illustrated using the following special characters for clarification. *Do not* type these characters on the command line:

| <> | required syntactical element |

|----|------------------------------|

| [] | optional field               |

| [] | repeated optional fields     |

- 2. Fields are separated by any number of space characters.

- 3. All numeric fields, unless noted otherwise, are interpreted as hexadecimal.

- 4. Command-line entries are case-insensitive and may be typed using any combination of upper- and lower-case letters.

- 5. A maximum of 80 characters, including the terminating carriage return, may be entered on the command line. After the 80th character, D-Bug12 automatically terminates the command-line entry and processes the characters entered to that point.

- 6. Before the <ENTER> or <RETURN> key is pressed, the command line may be edited using the backspace key. Receiving the backspace character causes D-Bug12 to delete the previously-received character from its input buffer and erase the character from the display.

#### 3.5.3 Command-Set Summary

Table 3-1 summarizes the D-Bug12 commands. For detailed descriptions of each command, refer to **3.6 D-Bug12 Command Set**.

Table 3-1. D-Bug12 Command-Set Summary

| Command                                                                   | Description                          |  |

|---------------------------------------------------------------------------|--------------------------------------|--|

| ASM <address></address>                                                   | Single-line assembler/disassembler   |  |

| BAUD <baudrate></baudrate>                                                | Set the SCI communications baud rate |  |

| BF <startaddress><endaddress> [<data>]</data></endaddress></startaddress> | Block fill user memory with data     |  |

| BR [ <address>&lt;]</address>                                             | Set/display user breakpoints         |  |

| BULK                                                                      | Bulk erase byte-erasable EEPROM      |  |

3-8 68EVB912BC32UM/D

Table 3-1. D-Bug12 Command-Set Summary (continued)

| Command                                                                                  | Description                                                                         |

|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------|

| CALL [ <address>]</address>                                                              | Execute a user subroutine; return to D-Bug12 when finished                          |

| DEVICE [see description]                                                                 | Select/define a new target MCU device                                               |

| EEBASE <address></address>                                                               | Inform D-Bug12 of the target's EEPROM base address                                  |

| FBULK                                                                                    | Erase the target processor's on-chip Flash EEPROM                                   |

| FLOAD <addressoffset></addressoffset>                                                    | Program the target processor's on-chip Flash EEPROM from S-Records                  |

| G [ <address>]</address>                                                                 | Go — begin execution of user program                                                |

| GT <address></address>                                                                   | Go Till — set a temporary breakpoint and begin execution of user program            |

| HELP                                                                                     | Display D-Bug12 command set and command syntax                                      |

| LOAD [ <addressoffset>]</addressoffset>                                                  | Load user program in S-Record format*                                               |

| MD <startaddress> [<endaddress>]</endaddress></startaddress>                             | Memory Display — display memory contents in hex bytes/ASCII format                  |

| MDW <startaddress> [<endaddress>]</endaddress></startaddress>                            | Memory Display Word — display memory contents in hex words/ASCII format             |

| MM <address> [<data>]</data></address>                                                   | Memory Modify — interactively examine/change memory contents                        |

| MMW <address> [<data>]</data></address>                                                  | Memory Modify Word — interactively examine/change memory contents                   |

| MOVE <startaddress> <endaddress> <destaddress></destaddress></endaddress></startaddress> | Move a block of memory                                                              |

| NOBR [ <address> <address>]</address></address>                                          | Remove individual user breakpoints                                                  |

| RD                                                                                       | Register Display — display the CPU register contents                                |

| REGBASE                                                                                  | Inform D-Bug12 of the target I/O register's base address                            |

| RESET                                                                                    | Reset the target CPU                                                                |

| RM                                                                                       | Register Modify — interactively examine/change CPU register contents                |

| STOP                                                                                     | Stop execution of user code on the target processor and place it in background mode |

68EVB912BC32UM/D 3-9

Table 3-1. D-Bug12 Command-Set Summary (continued)

| Command                                                        | Description                                                                   |

|----------------------------------------------------------------|-------------------------------------------------------------------------------|

| T [ <count>]</count>                                           | Trace — execute an instruction, disassemble it, and display the CPU registers |

| UPLOAD <startaddress> <endaddress></endaddress></startaddress> | Display memory contents in S-Record format*                                   |

| VERF [ <addressoffset>]</addressoffset>                        | Verify memory contents against S-Record Data                                  |

| <registername> <registervalue></registervalue></registername>  | Set CPU <registername> to <registervalue></registervalue></registername>      |

| * Refer to Appendix A for S-Record information.                |                                                                               |

# 3.6 D-BUG12 COMMAND SET

In the following command descriptions, the examples represent what is seen on the terminal display. For clarity, the user's entry is underlined. This underlining *does not actually appear onscreen*.

A typical example looks like this:

>baud 9600

Change Terminal BR, Press Return

D-Bug12's response

D-Bug12 prompt for next entry

3-10 68EVB912BC32UM/D

ASM Assembler/Disassembler ASM

syntax:

ASM <Address>

where:

<Address> is a 16-bit hexadecimal number.

The assembler/disassembler is an interactive memory editor that allows memory contents to be viewed and altered using assembly language mnemonics. Each entered source line is translated into object code and placed into memory at the time of entry. When displaying memory contents, each instruction is disassembled into its source mnemonic form and displayed along with the hexadecimal object code and any instruction operands.

Assembler mnemonics and operands may be entered in any mix of upper and lower case letters. Any number of spaces may appear between the assembler prompt and the instruction mnemonic or between the instruction mnemonic and the operand. Numeric values appearing in the operand field are interpreted as *signed* decimal numbers. Placing a \$ in front of any number will cause the number to be interpreted as a hexadecimal number.

When an instruction is disassembled and displayed, the DBug12 prompt is displayed following the disassembled instruction. If a carriage return is the first non-space character entered following the prompt, the next instruction in memory is disassembled and displayed on the next line.

If a CPU12 instruction is entered following the prompt, the entered instruction is assembled and placed into memory. The line containing the new entry is erased and the new instruction is disassembled and displayed on the same line. The next instruction location is then disassembled and displayed on the screen.

The instruction mnemonics and operand formats accepted by the assembler follows the syntax as described in the *CPU12 Reference Manual*.

There are a number of M68HC11 instruction mnemonics that appear in the *CPU12 Reference Manual* that do not have directly equivalent CPU12 instructions. These mnemonics, listed in Table 3-2, are translated into functionally equivalent CPU12 instructions. To aid the current M68HC11 users who may desire to continue using the M68HC11 mnemonics, the disassembler portion of the assembler/disassembler recognizes the functionally equivalent CPU12 instructions and disassembles those instructions into the equivalent M68HC11 mnemonics.

When entering branch instructions, the number placed in the operand field should be the absolute destination address of the instruction. The assembler calculates the two's-complement offset of the branch and places the offset in memory with the instruction

68EVB912BC32UM/D 3-11

The assembly/disassembly process may be terminated by entering a period (.) as the first non-space character following the assembler prompt.

#### restrictions:

None.

Table 3-2. M68HC11 to CPU12 Instruction Translation

| M68HC11 Mnemonic | CPU12 Instruction | M68HC11 Mnemonic                     | CPU12 Instruction                    |

|------------------|-------------------|--------------------------------------|--------------------------------------|

| CLC              | ANCC #\$FE        | INS                                  | LEAS 1, S                            |

| CLI              | ANCC #\$EF        | TAP                                  | TFR A, CC                            |

| CLV              | ANCC #\$FD        | TPA                                  | TFR CC, A                            |

| SEC              | ORCC # \$01       | TSX                                  | TFR S, X                             |

| SEI              | ORCC #\$10        | TSY                                  | TFR S, Y                             |

| SEV              | ORCC # \$02       | XGDX                                 | EXG D, X                             |

| ABX              | LEAX B, X         | XGDY                                 | EXG D, Y                             |

| ABY              | LEAY B, Y         | SEX R <sub>8</sub> , R <sub>16</sub> | TFR R <sub>8</sub> , R <sub>16</sub> |

| DES              | LEAS -1, S        |                                      |                                      |

#### example:

| ADM  | 000          |       |                                     |            |

|------|--------------|-------|-------------------------------------|------------|

| 0800 | CC1000       | LDD   | #\$1000                             |            |

| 0803 | 1803123401FE | MOVW  | #\$1234,\$01FE                      |            |

| 0809 | 0EF9800001F1 | BRSET | -32768,PC,\$01,\$0700               |            |

| 080F | 18FF         | TRAP  | \$FF                                |            |

| 0811 | 183FE3       | ETBL  | <illegal addr="" mode=""></illegal> | > <u>.</u> |

| >    |              |       |                                     |            |

#### assembly operand format:

>ASM 800

This section describes the operand format used by the assembler when assembling CPU12 instructions. The operand format accepted by the assembler is described separately in the *CPU12 Reference Manual*. Rather than describe the numeric format accepted for each instruction, some general rules are used. Exceptions and complicated operand formats are described separately.

In general, anywhere the assembler expects a numeric value in the operand field, either a decimal or hexadecimal value may be entered. Decimal numbers are entered as signed constants having a range of -32768 to 65535. A leading minus sign (-) indicates negative numbers, the absence of a leading minus

3-12 68EVB912BC32UM/D

sign indicates a positive number. A leading plus sign (+) is not allowed. Hexadecimal numbers must be entered with a leading dollar sign (\$) followed by one to four hexadecimal digits. The default number base is decimal.

For all branching instructions (Bcc, LBcc, BRSET, BRCLR, DBEQ, DBNE, IBEQ, IBNE, TBEQ, and TBNE), the number entered as the branch address portion of the operand field is the absolute address of the branch destination. The assembler calculates the two's-complement offset to be placed in the assembled object code.

### disassembly operand format:

The operand format used by the disassembler is described separately in the *CPU12 Reference Manual*. Rather than describing the numeric format used for each instruction, some general rules are applied. Exceptions and complicated operand formats are described separately.

All numeric values disassembled as hexadecimal numbers are preceded by a dollar sign (\$) to avoid being confused with values disassembled as signed decimal numbers.

For all branch (Bcc, LBcc, BRSET, BRCLR, DBEQ, DBNE, IBEQ, IBNE, TBEQ, TBNE) instructions the numeric value of the address portion of the operand field is displayed as the hexadecimal absolute address of the branch destination.

All offsets used with indexed addressing modes are disassembled as signed decimal numbers.

All addresses, whether direct or extended, are disassembled as four digit hexadecimal numbers.

All 8-bit mask values (BRSET/BRCLR/ANDCC/ORCC) are disassembled as two-digit hexadecimal numbers.

All 8-bit immediate values are disassembled as hexadecimal numbers.

All 16-bit immediate values are disassembled as hexadecimal numbers.

BAUD Set Baud Rate BAUD

syntax:

BAUD <BAUDRate>

where:

<BAUDRate> is an unsigned 16-bit decimal number.

The BAUD command is used to change the communications rate of the SCI used by D-Bug12 for the terminal interface.

#### restrictions:

Because the <BAUDRate> parameter supplied on the command line is a 16-bit unsigned integer, BAUD rates greater than 65535 baud cannot be set using this command. The SCI BAUD rate divider value for the requested BAUD rate is calculated using the Eclock value supplied in the DBug12 customization data area. Because the SCI BAUD rate divider is a 13-bit counter, certain BAUD rates may not be supported at particular E-clock frequencies. If the value calculated for the SCI's BAUD rate divider is equal to zero or greater than 8191, command execution is terminated and the communications BAUD rate is not changed.

#### example:

```

>BAUD 50

Invalid BAUD Rate

>BAUD 38400

Change Terminal BR, Press Return

>

```

3-14 68EVB912BC32UM/D

BF Block Fill BF

#### syntax:

BF <StartAddress> <EndAddress> [<Data>]

#### where:

<StartAddress> is a 16-bit hexadecimal number.

<EndAddress> is a 16-bit hexadecimal number.

<Data> is an 8-bit hexadecimal number.

The Block Fill command is used to place a single 8-bit value into a range of memory locations. <StartAddress> is the first memory location written with <data> and <EndAddress> is the last memory location written with <data>. If the <data> parameter is omitted, the memory range is filled with the value \$00.

### restrictions:

None.

### example:

```

>BF 6400 6fff 0

>BF 6f00 6fff 55

```

BR Breakpoint Set BR

syntax:

```

BR [<Address> <Address> ...]

```

where:

<Address> are optional 16-bit hexadecimal numbers.

The BR command is used to set a software breakpoint at a specified address or to display any previously set breakpoints. The function of a breakpoint is to halt user program execution when the program reaches the breakpoint address. When a breakpoint address is encountered, D-Bug12 disassembles the instruction at the breakpoint address, prints the CPU12's register contents, and waits for a D-Bug12 command to be entered by the user.

Breakpoints are set by typing the breakpoint command followed by one or more breakpoint addresses. Entering the breakpoint command without any breakpoint addresses will display all the currently set breakpoints.

A maximum of 10 user breakpoints may be set at one time.

#### restrictions:

D-Bug12 implements the breakpoint function by replacing the opcode at the breakpoint address in the users program with an SWI instruction when operating in EVB mode or with the BGND instruction when operating in POD mode. A breakpoint may not be set on a user SWI instruction when operating in EVB mode. In either mode, breakpoints may only be set at an opcode address, and breakpoints may only be placed at memory addresses in alterable memory.

Even though D-Bug12 supports a maximum of 10 user-defined breakpoints, a maximum of 9 breakpoints may be set on the command line at one time. This restriction is due to the limitation of the command-line processor, which allows a maximum of 10 command-line arguments, including the command string.

When operating in POD mode, new breakpoints may not be set with the BR command when the 'R>" prompt is displayed. However, the BR command may be used to display breakpoints that are currently set in the user's running program.

D-Bug12 version 2.0.0 does not support the MC68HC912BC32's hardware breakpoint (H/W) function. Later versions of D-Bug12, which may support this function, can be obtained from the sources listed in **Obtaining D-Bug12 Upgrades** on page E-5.

3-16 68EVB912BC32UM/D

><u>BR 35ec 2f80 c592</u> Breakpoints: 35EC 2F80 C592

Breakpoints: 35EC 2F80 C592

## **BULK**

### **Bulk Erase EEPROM**

**BULK**

#### syntax:

BULK

The BULK command is used to erase the entire contents of byte-erasable EEPROM in a single operation. After the bulk erase operation has been performed, each on-chip EEPROM location is checked for an erased condition.

#### restrictions:

In order to erase EEPROM, the EEPROM block-protect control bits must be cleared. Refer to the *MC68HC912BC32 Technical Summary* for locations and operation of the block-protect controls.

#### example:

>BULK

F/EEPROM Failed To Erase >BULK

>

CALL Call Subroutine CALL

syntax:

CALL [<Address>]

where:

<Address> is an optional 16-bit hexadecimal number.

The CALL command is used to execute a subroutine and return to the D-Bug12 monitor program when the final RTS of the subroutine is executed. When control is returned to D-Bug12, the CPU register contents are displayed. All CPU registers contain the values at the time the final RTS instruction was executed, with the exception of the program counter (PC). The PC contains the starting address of the subroutine. If a subroutine address is not supplied on the command line, the current value of the Program Counter (PC) is used as the starting address.

#### **NOTE:**

No user breakpoints are placed in memory before execution is transferred to user code.

#### restrictions:

If the called subroutine modifies the value of the stack pointer during its execution, it *must* restore the stack pointer's original value before executing the final RTS of the called subroutine. This restriction is required because a return address is placed on the users stack that returns to D-Bug12 when the final RTS of the subroutine is executed. Obviously, any subroutine must obey this restriction to execute properly.

The CALL command cannot be issued when the 'R>" prompt is displayed, indicating that the target system is already running a user program.

#### example:

```

>CALL 820

Subroutine Call Returned

РC

SP

Χ

Υ

D = A:B

CCR = SXHI

NZVC

0820

0A00

057C

0000

0F:F9

1001

0000

```

DEVICE Specify Target MCU Device DEVICE

syntax:

DEVICE

DEVICE <DeviceName> [<EEStart> <EEEnd> <FStart>

<FEnd> <RAMStart> <RAMEnd> <IOBase>]

where:

<DeviceName> is the maximum of 7 ASCII characters used to select/define a target

MCU device.

<EEStart> is the on-chip EEPROM starting address; a 16-bit hexadecimal

number.

<EEEnd> is the on-chip EEPROM ending address; a 16-bit hexadecimal number.

<FStart> is the on-chip Flash EEPROM starting address; a 16-bit hexadecimal

number.

<FEEnd> is the on-chip Flash EEPROM ending address; a 16-bit hexadecimal

number.

<RAMStart> is the on-chip RAM starting address; a 16-bit hexadecimal number.

<RAMEnd> is the on-chip RAM ending address; a 16-bit hexadecimal number.

<IOBase> is the base address of the on-chip I/O registers; a 16-bit hexadecimal

number.

Selecting the proper target MCU with the DEVICE command provides D-Bug12 the information necessary to allow transparent alteration of the target MCU's on-chip EEPROM using any D-Bug12 commands that modify memory. It also provides the necessary information to allow the programming and erasure of on-chip Flash EEPROM. In addition, it allows D-Bug12 to initialize the stack pointer to the top of on-chip RAM when the target MCU is reset by use of the RESET command. The DEVICE command has three separate command line formats that allows for the display, selection and/or definition of target device parameters.

Entering "DEVICE" on the command line followed by a carriage return displays the name of the currently selected device, the on-chip EEPROM's starting and ending address, the on-chip Flash EEPROM's starting and ending address, the on-chip RAM's starting and ending address, and the I/O Base address. This form of the command may be used when D-Bug12 is operating in either EVB or POD mode.

When D-Bug12 is operated in the POD mode, the DEVICE command may also be used to select or define a new target device. Entering the DEVICE command followed only by a device name configures

3-20 68EVB912BC32UM/D

D-Bug12 for operation with the selected target device. The default device list contains entries for the MC68HC912B32 and the MC68HC812A4. The MC68HC912B32 entry also supports the MC68HC912BC32. The table below shows the command line name to use for the two default MCU devices.

| Device Name | Target MCU   |  |  |

|-------------|--------------|--|--|

| 912B32      | MC68HC912B32 |  |  |

| 812A4       | MC68HC812A4  |  |  |

Entering the DEVICE command followed by a device name and seven hexadecimal parameters allows new devices to be added to the target device table or existing device table entries to be modified. When a new device is added or when an existing device entry is modified, it becomes the currently selected device. If a new device does not contain a particular on-chip resource, such as Flash EEPROM, a value of zero should be entered for the starting and ending addresses

Because the target device data and the current device selection are stored in the probe MCU's on-chip EEPROM, new device information and the device selection are retained when power is removed from the POD. If the M68EVB912BC32 is operated in EVB mode and the contents of *any* locations of the on-chip EEPROM are altered it is *strongly* recommended that the on-chip EEPROM be completely erased by using the BULK command before using the EVB in POD mode again. Erasing the on-chip EEPROM causes D-Bug12 to reinitialize the device table with the two default MCU devices. The information for any new devices that were added to the table will be lost.

#### restrictions:

When operating the M68EVB912BC32 in EVB mode, the DEVICE command may only be used to display the current device information.

The DEVICE command maintains a 16-bit checksum on the contents of the entire on-chip EEPROM to maintain the integrity of the device table. If any of the on-chip EEPROM locations are altered while operating the M68EVB912BC32 in EVB mode, D-Bug12 will reinitialize the device table with the default device information contained in the on-chip Flash EEPROM. However, it is possible for the checksum verification to fail (one case where the checksum will fail is if the entire contents of the on-chip EEPROM is programmed with zeros). Therefore, it is *strongly* recommended that the on-chip EEPROM be completely erased by using the BULK command before using the EVB in POD mode again. Using the EVB in Probe mode with a corrupt device data table may cause D-Bug12 to operate in an unpredictable manner.

The 768 bytes of on-chip EEPROM allows a total of 34 entries in the device table. *Do not* exceed this number.

When adding a new device to the device table, the addresses provided for the on-chip Flash EEPROM, on-chip RAM and the I/O Registers should reflect the locations of these resources when the part is reset. This requirement is necessary for the FBULK and FLOAD commands to work properly.

#### >DEVICE

Device: 912B32

EEPROM: \$0D00 - \$0FFF Flash: \$8000 - \$FFFF RAM: \$0800 - \$0BFF I/O Regs: \$0000

### S>DEVICE 912b32 1d00 1fff 8000 ffff 800 bff 0

Device: 912B32

EEPROM: \$1D00 - \$1FFF Flash: \$8000 - \$FFFF RAM: \$0800 - \$0BFF I/O Regs: \$0000

### S>DEVICE 812a4

Device: 812A4

EEPROM: \$1000 - \$1FFF RAM: \$0800 - \$0BFF I/O Regs: \$0000

S>

3-22 68EVB912BC32UM/D

### **EEBASE**

### Specify Target EEPROM Base Address

**EEBASE**

syntax:

EEBASE <Address>

where:

<Address> is an optional 16-bit hexadecimal number.

Each time D-Bug12 performs a memory write, it automatically performs the necessary register manipulations to program the on-chip EEPROM if the write operation falls within the address range of the target's on-chip EEPROM. Because user code may change the EEPROM's base address by writing to the INITEE register, D-Bug12 must be informed of the EEPROM's location if automatic EEPROM writes are to occur. The EEBASE command is used to specify the base address of the target processor's on-chip EEPROM.

When operating in EVB mode, the default EEPROM base address and range are specified in the customization data variables CustomData.EEBase and CustomData.EESize. The value in CustomData.EEBase is used by the startup code to remap the EEPROM. The EEBASE command may not be used to relocate the I/O registers.

When operating in POD mode, the target's default EEPROM base address and range are specified by the currently-selected device (See the DEVICE command for additional details).

The EEBASE command does *not* check to ensure that the parameter is a valid base address for the selected M68HC12 family member. If an improper base address is provided, automatic programming of the on-chip EEPROM will not operate properly.

#### **NOTE**

The EEBASE command does not automatically modify the INITEE register. It is the responsibility of the user to ensure that the INITEE register is modified either manually or through the execution of user code.

#### restrictions:

The EEBASE command may not be used when D-Bug12 is operated in EVB mode.

### S>DEVICE

Device: 912B32

EEPROM: \$0D00 - \$0FFF Flash: \$8000 - \$FFFF RAM: \$0800 - \$0BFF I/O Regs: \$0000

### S>EEBASE 1d00

Device: 912B32

EEPROM: \$1D00 - \$1FFF Flash: \$8000 - \$FFFF RAM: \$0800 - \$0BFF I/O Regs: \$0000

S>MM 12 0012 01 11 0013 0F <u>.</u> S>MD 1d00

3-24 68EVB912BC32UM/D

### **FBULK**

### Erase Target Flash EEPROM

**FBULK**

### syntax:

FBULK

The FBULK command is used to erase the entire contents of the target MCU's on-chip Flash EEPROM in a single operation. After the bulk erase operation has been performed, each on-chip Flash location is verified. If the contents are not \$FF, an error message is displayed.

The target processor's Flash EEPROM is erased by resetting the target processor and then loading a small driver program into the target processor's on-chip RAM. For this reason, the previous contents of the target processor's on-chip RAM are lost.

#### restrictions:

When operating in the EVB mode, the FBULK command cannot be used. If the FBULK command is entered while in EVB mode, an error message is displayed and command execution is terminated.

Before using the FBULK command, a target device must have been selected with the DEVICE command that reflects the locations of the target's on-chip Flash EEPROM, on-chip RAM, and the I/O registers when the part is reset. Failure to follow this restriction will cause the FBULK command to fail and may require that the EVB be reset.

Flash EEPROM programming voltage (Vpp) must be applied to the target MCU. If the target system is another M68EVB912BC32 board, Vpp may be supplied via header J13, with header J12 set accordingly. For more information on these EVB headers, see **Table 4-1**.

Because the FBULK command downloads a small "driver" program into the target MCU's on-chip RAM, DBug12's breakpoint table is cleared before beginning execution of the "driver". This is necessary to prevent previously-set breakpoints from accidentally halting the execution of the driver program.

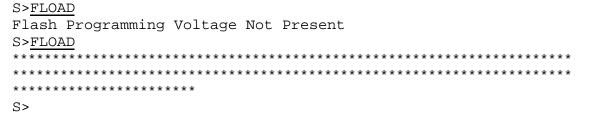

```

S>FBULK

Flash Programming Voltage Not Present

S>FBULK

F/EEPROM Failed To Erase

S>FBULK

S>

>FBULK

Command Not Allowed In EVB Mode

>

```

3-26 68EVB912BC32UM/D

### **FLOAD**

### Program Target Flash EEPROM

**FLOAD**

syntax:

FLOAD [<AddressOffset>]

where:

<AddressOffset>

is a 16-bit hexadecimal number.

The FLOAD command is used to program a target device's Flash EEPROM memory with the data contained in S-Record object files. The address offset, if supplied, is added to the load address of each S-Record before the S-Record's data bytes are placed in memory. Providing an address offset other than zero allows object code or data to be programmed into memory at a location other than that for which it was assembled or compiled.